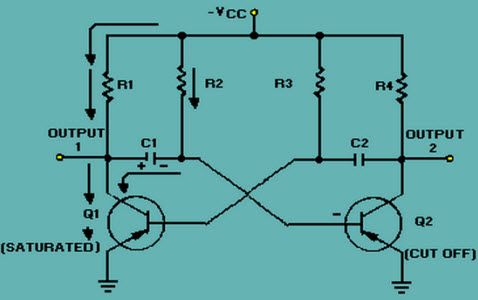

Dalam elektronik digital , Latch adalah salah satu jenis a litar logik , dan ia juga dikenali sebagai bistable-multivibrator . Kerana ia mempunyai dua keadaan stabil iaitu aktif tinggi dan juga rendah aktif. Ia berfungsi seperti peranti penyimpanan dengan menahan data melalui jalur maklum balas. Ia menyimpan 1-bit data selagi alat diaktifkan. Setelah diaktifkan diisytiharkan maka sekelip mata boleh menukar data yang disimpan. Ia sentiasa menguji input apabila isyarat yang diaktifkan diaktifkan. Kerja litar ini dapat dilakukan dalam 2 keadaan berdasarkan isyarat membolehkan tinggi atau rendah. Apabila latch kait dalam keadaan tinggi aktif, maka kedua-dua i / ps rendah. Begitu juga, apabila latch kait adalah keadaan rendah aktif, maka kedua-dua i / ps tinggi.

Jenis Selak yang berbeza

Selak boleh dikelaskan kepada pelbagai jenis yang merangkumi SR Latch, Selak G-Sated , D selak , Gated D Latch, JK Latch, dan T Latch.

SR Selak

Seorang Selak SR (Set / Reset) adalah alat tak segerak, dan berfungsi secara berasingan untuk isyarat kawalan dengan bergantung pada S-state & R-input. Latch SR menggunakan gerbang 2-NOR dengan sambungan gelung silang ditunjukkan di bawah. Selak ini boleh dibina dengan Gerbang NAND namun, kedua-dua input ditukar dan juga dibatalkan. Jadi ia dipanggil sebagai SR'-latch.

SR Selak

Setiap kali input tinggi diberikan ke garis-S kait, maka output Q akan menjadi tinggi. Dalam proses maklum balas, output Q akan tetap tinggi, apabila input S turun sekali lagi. Dengan cara ini, kait berfungsi sebagai alat memori.

Sama, input tinggi diberikan ke garis R kait, maka output Q menjadi rendah (dan tinggi Q '), maka memori kait akan diset semula dengan berkesan. Apabila kedua-dua input kait rendah, maka ia tetap dalam keadaan set awal atau keadaan semula. The jadual peralihan negeri atau jadual kebenaran selak SR ditunjukkan di bawah.

| S | R | Q | Q ’ |

| 0 | 0 | Selak | Selak |

0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

1 | 1 | 0 | 0 |

Apabila kedua-dua input tinggi sekaligus, ada masalah: ia diberitahu untuk menghasilkan Q & rendah Q secara bersamaan. Ini menghasilkan keadaan perlumbaan di litar sama ada flip flop dapat mencapai sesuatu yang berubah terlebih dahulu akan bertindak balas terhadap yang lain & menyatakan dirinya sendiri . Sebaiknya, kedua-duanya Gerbang logik sama dan peranti akan berada dalam keadaan tidak ditentukan untuk tahap yang tidak ditentukan.

Selak SR berpagar

Dalam beberapa kes, mungkin senang untuk dipesan ketika kait tidak dapat & tidak dapat mengunci. Sambungan ringkas sebuah Selak SR tidak lain dan tidak bukan selak SR berpagar . Ini memberikan garis Aktif yang harus didorong tinggi sebelum maklumat dapat dikunci. Walaupun garis kawalan diperlukan, kait tidak segerak kerana input yang dapat mengubah output walaupun di tengah-tengah denyut aktif.

Selak SR berpagar

Apabila input Enable rendah, o / ps dari gerbang juga mesti kurang, oleh itu output Q & Q tetap sesuai dengan maklumat sebelumnya. Cukup ketika i / p memungkinkan tinggi dapat mengubah posisi kait, seperti yang ditunjukkan dalam bentuk tabel. Seperti garis pengaktifan dinyatakan, SR-kait berpagar sama dalam proses menuju kait SR. Kadang kala, talian mengaktifkan adalah isyarat CLK namun, ini adalah strob baca / tulis.

CLK | S | R | Q (t + 1) |

0 | X | X | Q (t) (tiada perubahan) |

| 1 | 0 | 0 | Q (t) (tiada perubahan) |

1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

1 | 1 | 1 | X |

D Selak

Selak data adalah pengembangan mudah ke kait SR berpagar yang menghilangkan kemungkinan keadaan input yang tidak dapat diterima. Kerana kait SR berpagar memungkinkan kita mengikat output tanpa menggunakan input S atau R, kita dapat menghilangkan salah satu i / ps dengan menggerakkan kedua input dengan pemacu yang berlawanan. Kami menghilangkan satu input & secara automatik menjadikannya berlawanan dengan sisa input.

D Selak

Latch-D mengeluarkan input D ketika garis Enable tinggi, jika tidak, output adalah apa sahaja input D setiap kali input Enable terakhir tinggi. Inilah sebabnya ia dikenali sebagai selak telus. Apabila Enable dinyatakan, maka kait disebut sebagai lutsinar dan isyarat menyebar lurus melaluinya kerana jika tidak ada.

ADALAH | D | Q | Q ’ |

0 | 0 | Selak | Selak |

0 | 1 | Selak | Selak |

1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Selak Gated D

KE selak berpagar D dirancang hanya dengan menukar SR-latch berpagar, dan satu-satunya perubahan pada SR-latch berpagar adalah bahawa input R mesti diubah suai ke S. Latch kait tidak boleh dibentuk dari SR-kait menggunakan NOR ditunjukkan di bawah.

Selak Gated D

Apabila CLK diaktifkan sebaliknya tinggi, o / p mengunci apa sahaja yang terdapat pada input D. Begitu juga ketika CLK rendah, maka D i / p untuk akhir akhir tinggi adalah output.

CLK | D | Q (t + 1) |

| 0 | X | Q (t) |

1 | 0 | 0 |

| 1 | 1 | 1 |

Litar selak sama sekali tidak akan mengalami keadaan Perlumbaan kerana satu-satunya input D dibalikkan untuk ditawarkan kepada kedua-dua input. Oleh itu, tidak ada kemungkinan keadaan input serupa. Oleh itu litar D-latch dapat digunakan dengan selamat di beberapa litar.

JK Selak

Kedua-duanya Selak JK , serta kait RS, serupa. Selak ini terdiri daripada dua input iaitu J dan K yang ditunjukkan dalam rajah gerbang logik berikut. Dalam jenis selak ini, keadaan yang tidak jelas telah dikeluarkan di sini. Apabila input selak JK tinggi, output akan ditukar. Satu-satunya perbezaan yang dapat kita perhatikan di sini adalah maklum balas output terhadap input, yang tidak terdapat dalam kait RS.

JK Selak

T Selak

The Selak T dapat dibentuk setiap kali input selak JK dipendekkan. Fungsi T Latch akan menjadi seperti ini ketika input kait tinggi, dan kemudian output akan ditukar.

T Selak

Kelebihan Latches

The kelebihan selak sertakan perkara berikut.

- Reka bentuk selak sangat fleksibel jika dibandingkan dengan FF (sandal jepit)

- Selak menggunakan kuasa yang lebih sedikit.

- Prestasi selak dalam reka bentuk litar berkelajuan tinggi cepat kerana ini tidak segerak dalam reka bentuk dan tidak memerlukan isyarat CLK.

- Bentuk selaknya sangat kecil dan menempati kawasan yang kurang

- Sekiranya operasi litar berdasarkan kait tidak selesai dalam waktu yang ditentukan, mereka meminjam masa yang diperlukan dari yang lain untuk menyelesaikan operasi

- Latches memberikan penjadualan yang agresif apabila dibandingkan dengan litar flip-flop .

Kekurangan Latches

The kelemahan selak sertakan perkara berikut.

- Akan ada kemungkinan mempengaruhi keadaan perlumbaan, jadi ini tidak diharapkan.

- Apabila selak peka tahap, maka ada kemungkinan kestabilan meta.

- Menganalisis litar sukar kerana sifat sensitif tahap.

- Litar boleh diuji dengan menggunakan program CAD tambahan

Pemakaian Selak

The aplikasi selak sertakan perkara berikut.

- Secara amnya, selak digunakan untuk menjaga keadaan bit untuk mengekod nombor binari

- Latches adalah elemen penyimpanan bit tunggal yang banyak digunakan dalam pengkomputeran dan juga penyimpanan data.

- Latches digunakan dalam litar seperti power gating & clock sebagai alat simpanan.

- Selak D berlaku untuk sistem tak segerak seperti port input atau output.

- Selak data digunakan dalam sistem dua fasa segerak untuk mengurangkan jumlah transit.

Oleh itu, ini semua mengenai gambaran keseluruhan selak. Ini adalah blok bangunan untuk litar berurutan . Perancangan ini dapat dilakukan dengan menggunakan pintu logik. Pengoperasiannya bergantung terutamanya pada input fungsi mengaktifkan. Inilah soalan untuk anda, apakah dua keadaan kerja selak?