Proses merancang perkakasan digital telah berubah dengan pesat sejak beberapa tahun kebelakangan ini. Jadi, litar digital kecil dapat dilaksanakan dengan menggunakan PAL dan PLA. Setiap peranti digunakan untuk melaksanakan pelbagai litar yang tidak memerlukan lebih daripada bilangan i / ps, o / ps dan istilah produk yang ditawarkan dalam cip tertentu. Cip ini tidak mencukupi untuk ukuran yang cukup sederhana, biasanya menyokong bilangan input dan output yang tidak lebih daripada 32. Untuk merancang litar ini yang memerlukan lebih banyak input dan output, sama ada banyak PLA / PAL boleh digunakan atau jenis yang lebih berkelas cip boleh digunakan disebut CPLD (peranti logik kompleks yang dapat diprogramkan). Cip CPLD merangkumi beberapa blok litar pada satu cip dengan sumber pendawaian dalaman untuk memasang blok litar. Setiap blok litar setanding dengan PLA atau PAL.

Apakah Perisian Logik yang Boleh Diprogramkan?

Akronim CPLD adalah 'Perisian logik yang dapat diprogramkan kompleks', itu adalah satu jenis litar bersepadu bahawa pereka aplikasi merancang untuk melaksanakan perkakasan digital seperti telefon bimbit. Ini dapat menangani reka bentuk yang lebih tinggi daripada SPLD (peranti logik mudah diprogramkan), tetapi menawarkan logik yang lebih rendah daripada FPGA ( susunan gerbang yang boleh diprogramkan di lapangan ). CPLD merangkumi banyak blok logik setiap blok merangkumi 8-16 makrocell. Oleh kerana setiap blok logik melaksanakan fungsi tertentu, semua makrocell dalam blok logik dihubungkan sepenuhnya. Bergantung pada penggunaannya, blok-blok ini mungkin atau tidak dapat dihubungkan antara satu sama lain.

Peranti Logik Boleh Diprogramkan Kompleks

Sebilangan besar CPLD (peranti logik yang dapat diprogramkan kompleks) mempunyai makrocell dengan jumlah fungsi logik dan pilihan FF (flip-flop) . Bergantung pada cip, fungsi logik gabungan menyokong 4 hingga 16 istilah produk dengan penggemar masuk. CPLD juga berbeza dari segi pergeseran register dan gerbang logik. Kerana alasan ini, CPLD dengan sebilangan besar gerbang logik boleh digunakan sebagai ganti FPGA. Spesifikasi CPLD yang lain menunjukkan jumlah istilah produk yang dapat dicapai oleh makrocell. Istilah produk adalah produk isyarat digital yang melaksanakan fungsi logik tertentu.

CPLD tersedia dalam beberapa bentuk pakej IC dan keluarga logik. CPLD juga berbeza dari segi voltan bekalan, arus operasi, arus siap sedia dan pelesapan kuasa. Di samping itu, ini dapat diperoleh dengan pelbagai jumlah memori dan pelbagai jenis sokongan memori. Biasanya, memori dinyatakan dalam bit / megabit. Sokongan memori terdiri daripada ROM, RAM dan RAM dwi-port. Ia juga terdiri daripada memori CAM (memori yang dapat diatasi kandungan) dan juga memori FIFO (first-in, first-out) dan memori LIFO (last-in, last-out).

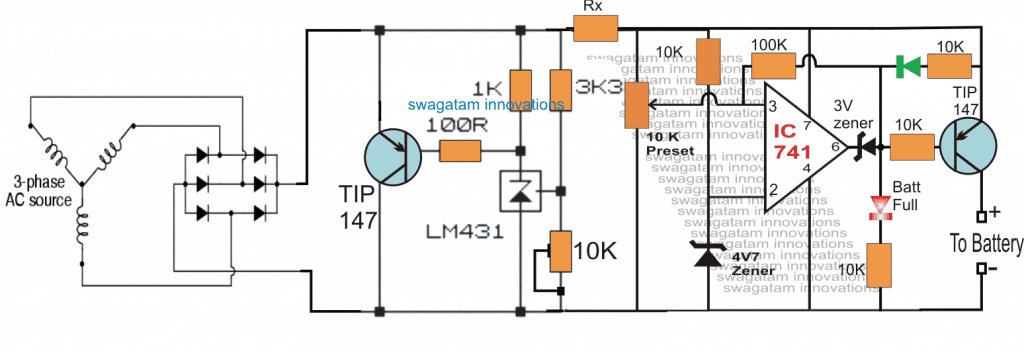

Senibina Peranti Logik yang Boleh Diprogramkan Kompleks

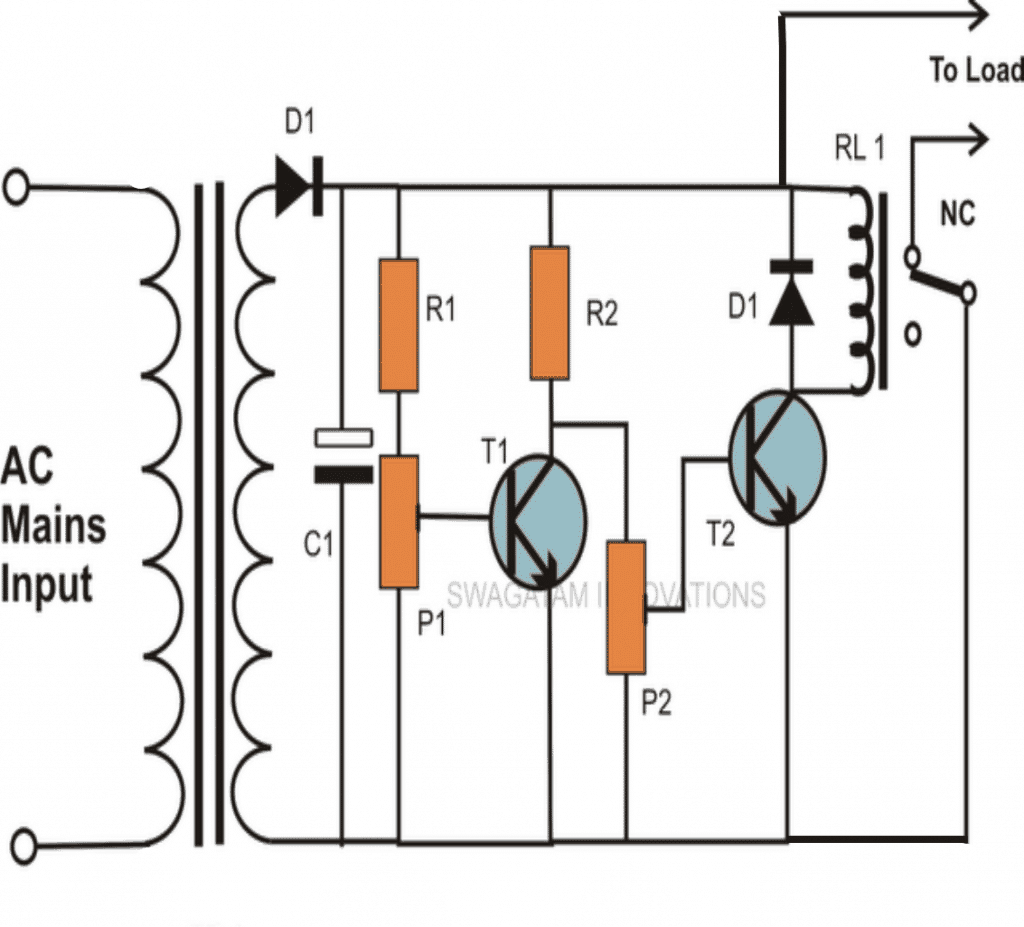

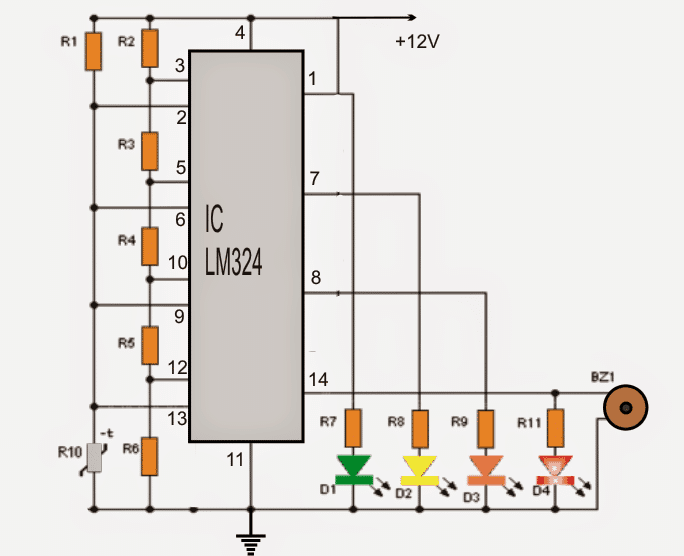

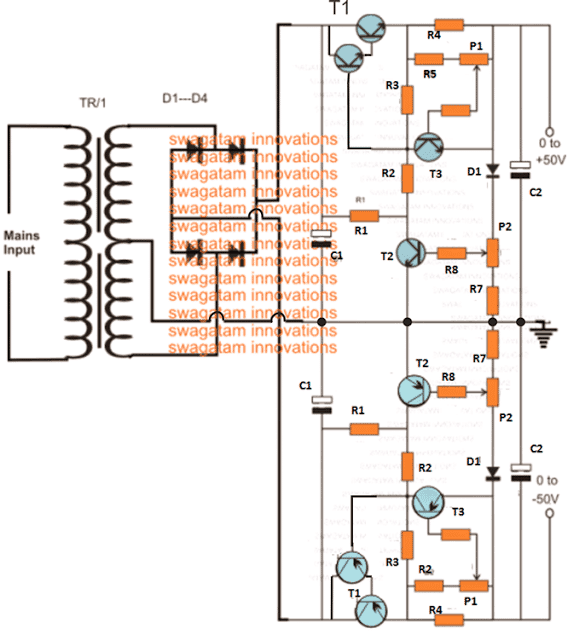

Peranti logik yang boleh diprogramkan kompleks terdiri daripada sekumpulan FB yang dapat diprogramkan (blok berfungsi). Input dan output blok fungsional ini dihubungkan bersama oleh GIM (matriks interkoneksi global). Matriks interkoneksi ini dapat dikonfigurasikan semula, sehingga kami dapat mengubah suai hubungan antara blok berfungsi. Akan ada beberapa blok input dan output yang memungkinkan kita menyatukan CPLD dengan dunia luar. Senibina CPLD ditunjukkan di bawah.

Secara amnya, FB yang boleh diprogramkan kelihatan seperti susunan gerbang logik , di mana susunan gerbang AND dapat diprogramkan dan gerbang OR stabil. Tetapi, setiap pengeluar mempunyai cara berfikir untuk merancang blok berfungsi. O / p yang tersenarai dapat dijumpai dengan mengoperasikan isyarat maklum balas yang diperoleh dari output gerbang OR.

Senibina CPLD

Dalam pengaturcaraan CPLD, reka bentuk pertama kali dikodkan dalam bahasa Verilog atau VHDL setelah kodnya (disimulasikan dan disintesis. Semasa sintesis, model CPLD (peranti sasaran) dipilih sendiri dan senarai pemetaan berdasarkan teknologi dihasilkan. Senarai ini boleh ditutup -sesuai dengan seni bina CPLD yang asli menggunakan proses tempat dan laluan, biasanya dicapai oleh perisian tempat-dan-laluan milik syarikat CPLD Syarikat. Kemudian pengendali akan melakukan beberapa proses pengesahan. Sekiranya semuanya baik, dia akan menggunakan CPLD, jika tidak dia akan menyusunnya semula.

Isu Senibina CPLD

Apabila mempertimbangkan peranti logik yang dapat diprogram untuk digunakan dalam reka bentuk, ada beberapa masalah seni bina berikut yang dapat dipertimbangkan

- Teknologi pengaturcaraan

- Keupayaan blok fungsi

- Keupayaan I / O

Beberapa keluarga CPLD dari peruncit yang berbeza termasuk

- Altera MAX 7000 dan MAX 9000 keluarga

- Keluarga Atmel ATF dan ATV

- Keluarga LSI isp Lattice

- Kekisi (Vantis) MACH keluarga

- Keluarga Xilinx XC9500

Keluarga CPLD

Aplikasi CPLD

Aplikasi CPLD merangkumi yang berikut

- Peranti logik yang dapat diprogramkan kompleks sesuai untuk aplikasi kawalan kritikal berprestasi tinggi.

- CPLD dapat digunakan dalam reka bentuk digital untuk menjalankan fungsi boot loader

- CPLD digunakan untuk memuatkan data konfigurasi array gerbang yang dapat diprogramkan dari memori yang tidak mudah berubah.

- Secara amnya, ini digunakan dalam aplikasi reka bentuk kecil seperti penyahkodan alamat

- CPLD sering digunakan banyak aplikasi seperti sensitif kos, peranti mudah alih yang dikendalikan oleh bateri kerana ukurannya yang rendah dan penggunaan daya yang rendah.

Oleh itu, ini semua berkaitan dengan seni bina peranti logik yang boleh diprogramkan dan aplikasinya. Kami harap anda mendapat pemahaman yang lebih baik mengenai konsep ini. Selanjutnya, sebarang pertanyaan mengenai konsep ini atau untuk melaksanakan sebarang projek elektrik dan elektronik , sila berikan cadangan berharga anda dengan memberi komen di bahagian komen di bawah. Berikut adalah soalan untuk anda, apakah perbezaan antara CPLD dan FPGA?

Kredit Foto:

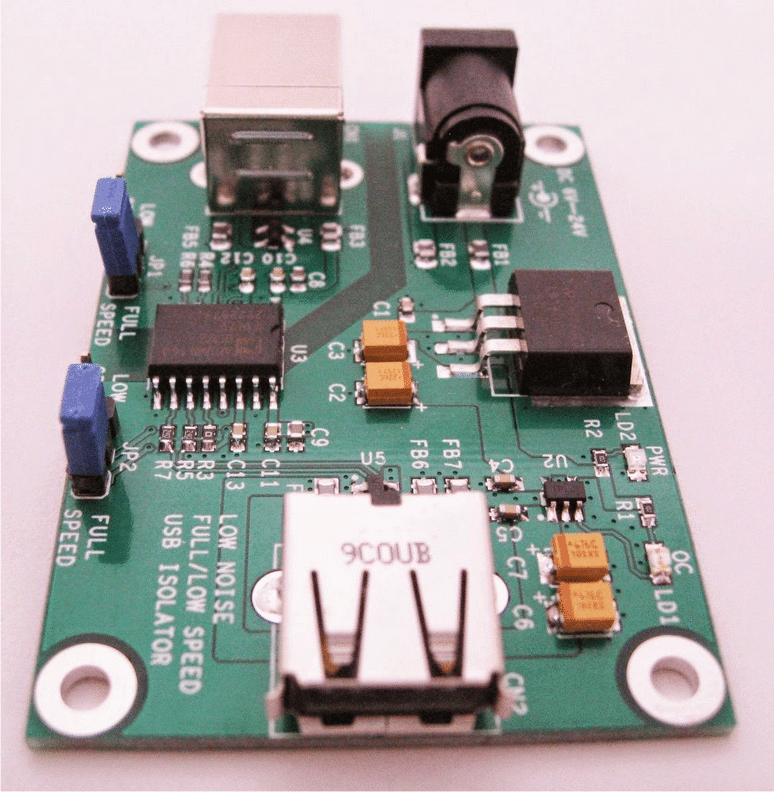

- CPLD wikimedia

- Senibina CPLD slidesharecdn