Secara sederhana, bias dalam BJT dapat didefinisikan sebagai proses di mana BJT diaktifkan atau dihidupkan dengan menerapkan magnitud DC yang lebih kecil di seberang terminal pangkalan / pemancarnya sehingga mampu melakukan DC yang lebih besar terminal pemancar pengumpulnya.

Kerja transistor Bipolar atau BJT pada tahap DC ditentukan oleh beberapa faktor, yang merangkumi pelbagai titik operasi melebihi ciri-ciri peranti.

Di bawah bahagian 4.2 yang dijelaskan dalam artikel ini, kami akan memeriksa perincian mengenai kisaran ini titik operasi untuk penguat BJT. Setelah bekalan DC yang ditentukan dikira, reka bentuk litar dapat dibuat untuk menentukan titik operasi yang diperlukan.

Pelbagai konfigurasi seperti itu diperiksa dalam artikel ini. Setiap model yang dibincangkan juga akan mengenal pasti kestabilan pendekatan, yang bermaksud, betapa sensitifnya sistem terhadap parameter tertentu.

Walaupun banyak rangkaian diperiksa dalam bahagian ini, mereka mempunyai satu persamaan mendasar antara penilaian setiap konfigurasi, kerana penggunaan berulang dari hubungan asas penting berikut:

Dalam kebanyakan keadaan, IB semasa asas adalah kuantiti pertama yang perlu ditentukan. Setelah IB dikenal pasti, hubungan Persamaan. (4.1) melalui (4.3) dapat dilaksanakan untuk mendapatkan sisa jumlah yang dimaksud.

Kemiripan dalam penilaian akan dapat dilihat dengan cepat ketika kita maju dengan bahagian berikutnya.

Persamaan untuk IB sangat serupa untuk banyak reka bentuk sehingga satu formula dapat berasal dari yang lain dengan hanya membuang atau memasukkan satu atau dua elemen.

Objektif utama bab ini adalah untuk mewujudkan tahap pemahaman mengenai transistor BJT yang akan membolehkan anda melaksanakan analisis DC mengenai litar mana-mana litar yang mempunyai penguat BJT sebagai elemen.

4.2 POINT OPERASI

Perkataan itu berat sebelah muncul dalam judul artikel ini adalah istilah mendalam yang menandakan pelaksanaan voltan DC, dan untuk menentukan tahap arus dan voltan tetap dalam BJT.

Untuk penguat BJT, arus dan voltan dc yang dihasilkan menghasilkan titik operasi pada ciri-ciri yang membentuk kawasan yang menjadi ideal untuk penguatan isyarat yang diperlukan. Oleh kerana titik operasi kebetulan merupakan titik yang telah ditentukan pada ciri-ciri, ia juga dapat disebut sebagai titik diam (disingkat sebagai titik-Q).

'Sunyi' dengan definisi menandakan keheningan, keheningan, tidak bergerak. Rajah 4.1 menunjukkan ciri output standard BJT yang mempunyai 4 titik operasi . Litar biasing dapat dikembangkan untuk mewujudkan BJT di salah satu titik ini atau yang lain di dalam kawasan aktif.

Peringkat maksimum ditunjukkan pada ciri-ciri Rajah 4.1 melalui garis mendatar untuk ICmax arus pengumpul tertinggi dan garis tegak lurus pada voltan pengumpul-ke-pemancar tertinggi VCEmax.

Batasan daya maksimum dikenal pasti dari lengkungan PCmax dalam rajah yang sama. Di hujung bawah grafik kita dapat melihat kawasan pemotongan, yang dikenal pasti oleh IB ≤ 0μ, dan kawasan tepu, yang dikenal pasti oleh VCE ≤ VCEsat.

Unit BJT mungkin boleh menjadi berat sebelah di luar had maksimum yang ditunjukkan ini, tetapi akibat dari proses tersebut akan mengakibatkan kemerosotan yang signifikan terhadap umur perangkat atau kerusakan total perangkat.

Mengehadkan nilai antara kawasan aktif yang ditunjukkan, seseorang dapat memilih pelbagai kawasan operasi atau titik . Titik Q yang dipilih biasanya bergantung pada spesifikasi litar yang dimaksudkan.

Namun, kita pasti dapat mempertimbangkan beberapa perbezaan antara jumlah poin yang digambarkan dalam Gambar 4.1 untuk memberikan beberapa cadangan asas mengenai titik operasi , dan oleh itu, litar bias.

Sekiranya tidak ada bias yang berlaku, peranti pada mulanya akan tetap dimatikan sepenuhnya, menyebabkan titik Q berada di A - iaitu, arus sifar melalui peranti (dan 0V melintasi). Oleh kerana penting untuk memihak BJT untuk membolehkannya bertindak balas untuk pelbagai isyarat input yang diberikan, titik A mungkin tidak sesuai.

Untuk titik B, apabila isyarat disambungkan ke litar, peranti akan menunjukkan variasi arus dan voltan melalui titik operasi , membolehkan peranti bertindak balas (dan mungkin menguatkan) kedua-dua aplikasi positif dan negatif dari isyarat input.

Apabila isyarat input digunakan secara optimum, voltan dan arus BJT mungkin akan berubah ..... namun mungkin tidak mencukupi untuk mengaktifkan peranti menjadi pemotongan atau ketepuan.

Titik C mungkin membantu penyimpangan positif dan negatif tertentu dari isyarat output, tetapi magnitud puncak ke puncak mungkin dibatasi pada jarak VCE = 0V / IC = 0 mA.

Bekerja pada titik C juga boleh menyebabkan sedikit kebimbangan mengenai ketidaklinieran kerana hakikat bahawa jurang antara lengkung IB dapat berubah dengan cepat di kawasan tertentu ini.

Secara umum, jauh lebih baik untuk mengoperasikan peranti di mana keuntungan peranti agak konsisten (atau linier), untuk menjamin bahawa penguatan pada ayunan keseluruhan isyarat input tetap seragam.

Titik B adalah wilayah yang memperlihatkan jarak linier yang lebih tinggi dan untuk itu aktiviti linier yang lebih besar, seperti yang ditunjukkan pada Gambar 4.1.

Titik D menetapkan peranti titik operasi hampir dengan tahap voltan dan kuasa tertinggi. Oleh itu, ayunan voltan keluaran pada had positif dibatasi apabila voltan maksimum tidak seharusnya dilampaui.

Titik B hasilnya kelihatan sempurna titik operasi berkenaan dengan keuntungan linear dan kemungkinan voltan dan arus yang paling besar.

Kami akan menerangkannya secara ideal untuk penguat isyarat kecil (Bab 8) namun, tidak selalu untuk penguat kuasa, .... kita akan membincangkannya kemudian.

Dalam wacana ini, saya akan memfokuskan pada bias transistor berkenaan dengan fungsi penguat isyarat kecil.

Terdapat satu lagi faktor bias yang sangat penting yang perlu dilihat. Setelah menentukan dan berat sebelah BJT dengan ideal titik operasi , kesan suhu juga harus dinilai.

Julat haba akan menyebabkan sempadan peranti seperti kenaikan arus transistor (ac) dan arus kebocoran transistor (ICEO) menyimpang. Julat suhu yang meningkat akan menyebabkan arus kebocoran yang lebih besar di BJT, dan dengan demikian akan mengubah spesifikasi operasi yang ditetapkan oleh rangkaian biasing.

Ini menunjukkan bahawa corak rangkaian juga perlu memfasilitasi tahap kestabilan suhu untuk memastikan bahawa kesan variasi suhu dengan peralihan minimum dalam titik operasi . Pemeliharaan titik operasi ini dapat ditentukan dengan faktor kestabilan, S, yang menandakan tahap penyimpangan pada titik operasi yang disebabkan oleh perubahan suhu.

Litar stabil yang optimum disarankan, dan ciri stabil beberapa litar bias penting akan dinilai di sini. Agar BJT menjadi berat sebelah dalam kawasan operasi linear atau berkesan, titik yang diberikan di bawah mesti dipuaskan:

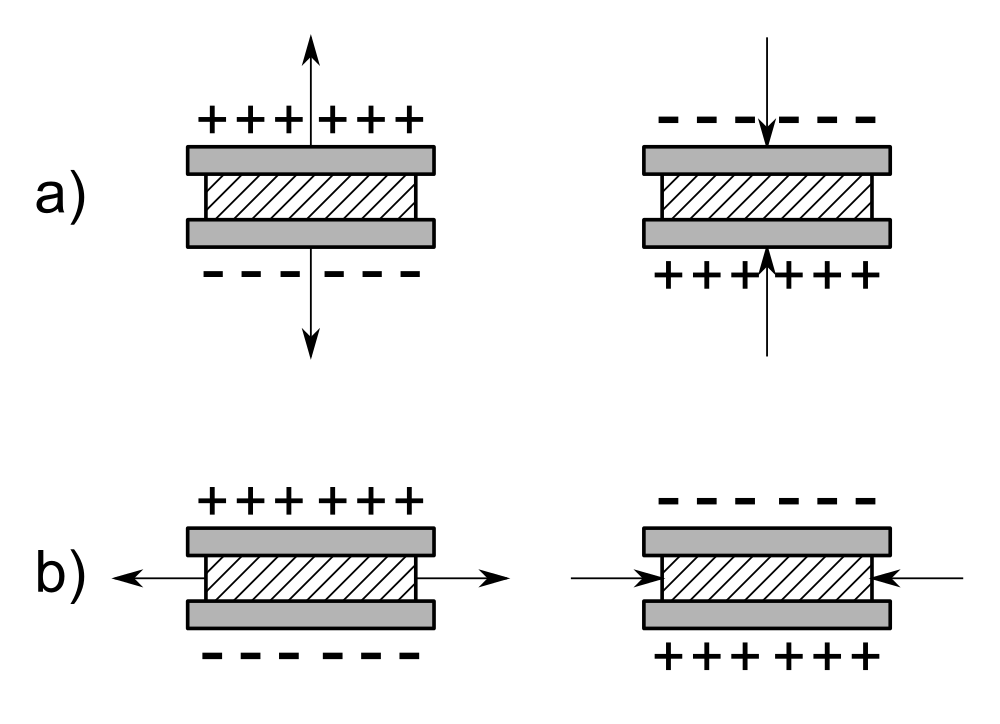

1. Persimpangan pemancar asas harus bias ke hadapan (voltan rantau p sangat positif), yang membolehkan voltan bias ke hadapan sekitar 0.6 hingga 0.7 V.

2. Persimpangan pemungut pangkalan mestilah bias terbalik (n-rantau sangat positif), dengan voltan bias terbalik tetap pada beberapa nilai di dalam had maksimum BJT.

[Ingat bahawa untuk bias ke hadapan voltan di persimpangan p-n akan hlm -positif, dan untuk bias terbalik ia adalah sebaliknya n -positif. Tumpuan pada huruf pertama ini harus memberi anda cara untuk mengingat polariti voltan penting dengan mudah.]

Operasi di kawasan cut-off, saturation, dan linear dari ciri BJT biasanya ditunjukkan seperti yang dijelaskan di bawah:

1. Operasi rantau linear:

Persimpangan pemancar asas ke depan berat sebelah

Persimpangan pemungut asas terbalik

2. Operasi kawasan pemotongan:

Persimpangan pemancar asas terbalik

3. Operasi wilayah tepu:

Persimpangan pemancar asas ke depan berat sebelah

Persimpangan pemungut asas ke depan berat sebelah

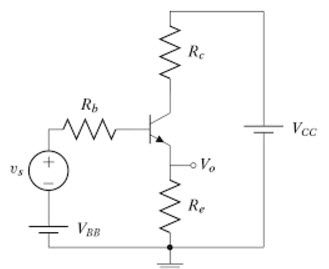

4.3 LITAR BIASA TETAP

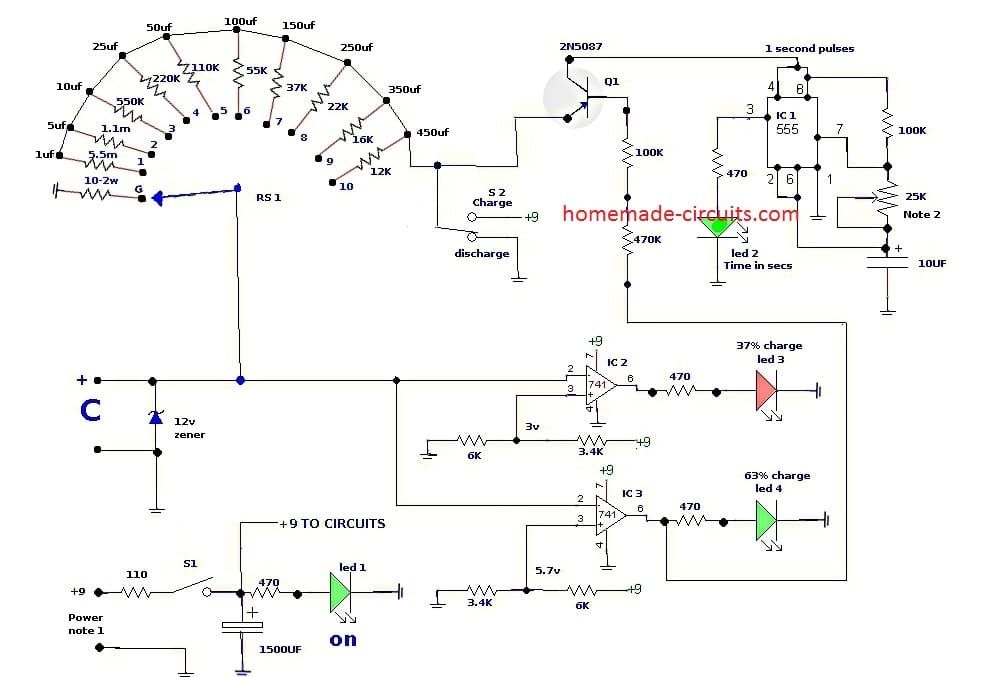

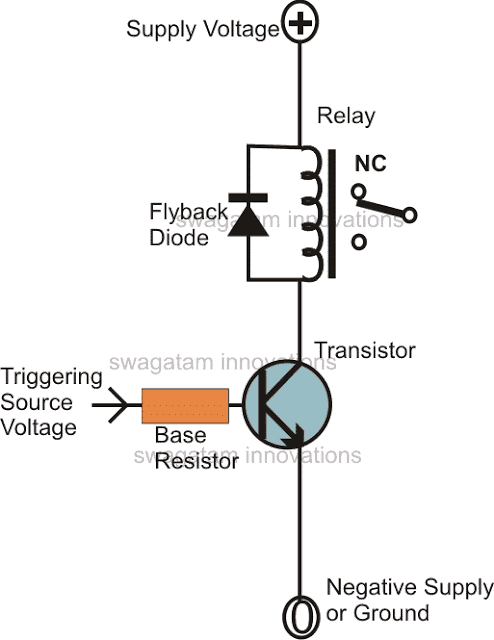

Litar bias tetap pada Rajah 4.2 dirancang dengan gambaran keseluruhan analisis bias transistor dc yang agak mudah dan tidak rumit.

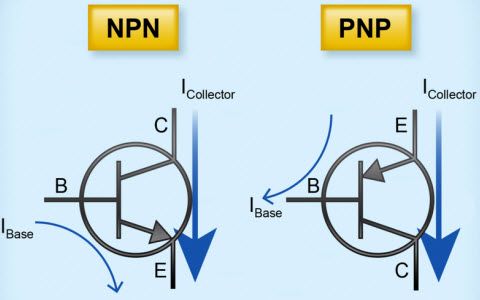

Walaupun rangkaian mengimplementasikan transistor NPN, formula dan pengiraannya dapat berfungsi sama efektif dengan penyediaan transistor PNP hanya dengan mengkonfigurasi semula jalur aliran dan polariti voltan semasa.

Arahan semasa Gambar 4.2 adalah arah arus sebenar, dan voltan dikenal pasti oleh anotasi langganan ganda sejagat.

Untuk analisis dc reka bentuk boleh dipisahkan dari tahap AC yang disebutkan hanya dengan menukar kapasitor dengan setara litar terbuka.

Lebih-lebih lagi, bekalan DC VCC dapat dibagi menjadi beberapa persediaan yang terpisah (hanya untuk melakukan penilaian) seperti yang terbukti pada Gambar 4.3 hanya untuk memungkinkan putus rangkaian input dan output.

Apa yang dilakukan ini adalah meminimumkan hubungan antara keduanya dengan IB arus asas. Perpisahan itu tidak diragukan lagi sah, seperti ditunjukkan pada Gambar 4.3 di mana VCC dihubungkan terus ke RB dan RC seperti pada Gambar 4.2.

Bias Maju Pangkalan – Pemancar

Mari kita menganalisis gelung litar pemancar asas yang ditunjukkan di atas dalam Rajah 4.4. Sekiranya kita melaksanakan persamaan voltan Kirchhoff mengikut arah jam untuk gelung, kita memperoleh persamaan berikut:

Kita dapat melihat bahawa kekutuban voltan jatuh merentasi RB seperti yang ditentukan melalui arah IB semasa. Menyelesaikan persamaan untuk IB semasa memberi kami hasil berikut:

Persamaan (4.4)

Persamaan (4.4) pastinya persamaan yang dapat dihafal dengan mudah, hanya dengan mengingat bahawa arus asas di sini menjadi arus yang melewati RB, dan dengan menerapkan hukum Ohm yang mana arus sama dengan voltan merentasi RB dibahagi dengan RB rintangan .

Voltan merentasi RB adalah voltan VCC yang berlaku di satu hujung ditolak penurunan di persimpangan asas ke pemancar (VBE).

Juga, kerana fakta bahawa bekalan VCC dan voltan pemancar asas VBE adalah jumlah tetap, pilihan resistor RB di pangkalan menetapkan jumlah arus asas untuk tahap pensuisan.

Pengumpul – Gelung Pemancar

Gambar 4.5 menunjukkan tahap litar pemancar pemungut, di mana arah IC semasa dan kekutuban yang sepadan dengan RC telah ditunjukkan.

Nilai arus pemungut dapat dilihat berkaitan langsung dengan IB melalui persamaan:

Persamaan (4.5)

Anda mungkin menarik untuk melihat bahawa kerana arus asas bergantung pada kuantiti RB, dan IC dihubungkan dengan IB melalui pemalar β, besarnya IC bukanlah fungsi dari rintangan RC.

Menyelaraskan RC ke nilai lain tidak akan menghasilkan kesan pada tahap IB atau bahkan IC, selagi wilayah aktif BJT dikekalkan.

Walaupun begitu, anda akan mendapati bahawa besarnya VCE ditentukan oleh tahap RC, dan ini mungkin merupakan perkara penting untuk dipertimbangkan.

Sekiranya kita menggunakan undang-undang voltan Kirchhoff mengikut arah pusingan mengikut arah putaran tertutup yang ditunjukkan dalam rajah 4.5, ia menghasilkan dua persamaan berikut:

Persamaan (4.6)

Ini menunjukkan bahawa voltan melintasi pemancar pemungut BJT dalam litar bias tetap adalah voltan bekalan yang setara dengan penurunan yang terbentuk merentasi RC

Untuk melihat sekilas notasi langganan tunggal dan ganda, ingatlah bahawa:

VCE = VC - VE -------- (4.7)

di mana VCE menunjukkan voltan yang mengalir dari pemungut ke pemancar, VC dan VE adalah voltan yang mengalir dari pemungut dan pemancar ke arah tanah masing-masing. Tetapi di sini, sejak VE = 0 V, kita ada

VCE = VC -------- (4.8)

Juga kerana kita mempunyai,

VBE = VB - DAN -------- (4.9)

dan kerana VE = 0, akhirnya kami mendapat:

VBE = VB -------- (4.10)

Harap ingat perkara berikut:

Semasa mengukur tahap voltan seperti VCE, pastikan meletakkan probe merah voltmeter pada pin pemungut dan probe hitam pada pin pemancar seperti yang ditunjukkan dalam gambar berikut.

VC menandakan voltan yang mengalir dari pemungut ke tanah dan prosedur pengukurannya juga seperti yang diberikan dalam gambar berikut.

Dalam kes ini, kedua-dua bacaan di atas akan serupa, tetapi untuk rangkaian litar yang berlainan, ia dapat menunjukkan hasil yang berbeza-beza.

Ini menunjukkan bahawa perbezaan pembacaan antara kedua-dua pengukuran tersebut dapat membuktikan penting ketika mendiagnosis kemungkinan kesalahan dalam rangkaian BJT.

Menyelesaikan Contoh Bias BJT Praktikal

Nilaikan yang berikut untuk konfigurasi bias tetap pada Rajah 4.7.

Diberikan:

(a) IBQ dan ICQ.

(b) VCEQ.

(c) VB dan VC.

(d) VBC.

Pada bab seterusnya kita akan belajar mengenai Ketepuan BJT.

Rujukan

Sepasang: Litar Bawah Pengawal Urutan Logik KE BAWAH Seterusnya: Apa itu Ketepuan Transistor