Dalam litar gabungan, gerbang logik yang berbeza digunakan untuk merancang pengekod, multiplexer, decoder & de-multiplexer. Litar ini mempunyai beberapa ciri seperti output litar ini terutama bergantung pada tahap yang ada di terminal input pada bila-bila masa. Litar ini tidak termasuk memori. Keadaan input yang lebih awal tidak mempunyai pengaruh terhadap keadaan semasa litar ini. Input dan output litar gabungan adalah ‘n’ no. input & ‘m’ tidak. daripada output. Sebilangan litar kombinasional adalah separuh penambah dan penambah penuh, penolak, pengekod, penyahkod, multiplexer, dan demultiplexer. Artikel ini membincangkan gambaran keseluruhan setengah penambah dan penambah penuh dan ia berfungsi dengan jadual kebenaran.

Apa itu Adder?

Penambah ialah litar logik digital dalam elektronik yang digunakan secara meluas untuk penambahan nombor. Di banyak komputer dan jenis pemproses lain, penambah bahkan digunakan untuk mengira alamat dan aktiviti yang berkaitan dan mengira indeks jadual di ALU dan bahkan digunakan di bahagian lain pemproses. Ini boleh dibina untuk banyak perwakilan berangka seperti perpuluhan kelebihan 3 atau kod binari. Penambah pada dasarnya dikelaskan kepada dua jenis: Half Adder dan Full Adder.

Apa itu Litar Penambah Setengah dan Penambah Penuh?

Litar penambah separuh mempunyai dua input: A dan B, yang menambah dua digit input dan menghasilkan nilai bawa dan jumlah. Litar penambah penuh mempunyai tiga input: A dan C, yang menambah tiga nombor input dan menghasilkan nilai tambah dan jumlah. Artikel ini memberikan maklumat terperinci mengenai apa tujuan setengah penambah dan penambah penuh dalam bentuk jadual dan juga dalam gambarajah litar. Telah disebutkan bahawa tujuan utama dan penting penambah adalah penambahan. Berikut adalah terperinci teori half adder dan full adder.

Penambah Setengah Asas dan Penambah Penuh

Separuh Penambah

Oleh itu, datang ke senario half adder, ia menambah dua digit binari di mana bit input disebut sebagai augend dan addend dan hasilnya akan menjadi dua output satu adalah jumlah dan yang lain dibawa. Untuk melakukan operasi penjumlahan, XOR diterapkan pada kedua input, dan pintu gerbang AND diterapkan pada kedua input untuk menghasilkan carry.

Rajah Fungsi HA

Manakala di litar penambah penuh, ia menambah 3 nombor satu bit, di mana dua dari tiga bit dapat disebut sebagai operan dan yang lain disebut sebagai bit dibawa masuk. Output yang dihasilkan adalah output 2-bit dan ini dapat disebut sebagai output membawa dan jumlah.

Dengan menggunakan setengah penambah, anda boleh merancang penambahan sederhana dengan bantuan pintu logik.

Mari kita lihat contoh penambahan dua bit tunggal.

2-bit jadual kebenaran separuh penambah adalah seperti di bawah:

Jadual Kebenaran Separuh Penambah

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

Ini adalah kombinasi bit tunggal yang paling tidak mungkin. Tetapi hasil untuk 1 + 1 adalah 10, hasil jumlahnya mesti ditulis semula sebagai output 2-bit. Oleh itu, persamaan boleh ditulis sebagai

0 + 0 = 00

0 + 1 = 01

1 + 0 = 01

1 + 1 = 10

Keluaran ‘1’of‘ 10 ’dilaksanakan. ‘SUM’ adalah output normal dan ‘CARRY’ adalah pelaksanaan.

Sekarang telah dijelaskan bahawa penambah 1-bit dapat dengan mudah dilaksanakan dengan bantuan Gerbang XOR untuk output 'SUM' dan Gerbang DAN untuk 'Carry'.

Sebagai contoh, apabila kita perlu menambahkan, dua bait 8-bit bersama-sama, maka ia dapat dilaksanakan dengan menggunakan rangkaian logik penambah penuh. Penambah separuh berguna apabila anda mahu menambah satu digit digit binari.

Cara untuk mengembangkan penambah digit dua-binari adalah dengan membuat jadual kebenaran dan mengurangkannya. Apabila anda ingin membuat penambah tiga digit biner, operasi penambahan setengah penambah dilakukan dua kali. Dengan cara yang serupa, apabila anda memutuskan untuk membuat penambah empat digit, operasi dilakukan sekali lagi. Dengan teori ini, jelas bahawa pelaksanaannya sederhana, tetapi pengembangan adalah proses yang memakan masa.

Ungkapan paling ringkas menggunakan fungsi ATAU eksklusif:

Jumlah = A XOR B

Carry = A DAN B

Diagram Logik HA

Dan ungkapan yang setara dari segi asas AND, OR, dan NOT adalah:

SUM = A.B + A.B ’

Kod VHDL Untuk Separuh Penambah

Entiti ha adalah

Pelabuhan (a: dalam STD_LOGIC

b: dalam STD_LOGIC

sha: keluar STD_LOGIC

cha: keluar STD_LOGIC)

akhir ha

Tingkah Laku Senibina litar di atas adalah

bermula

sha<= a xor b

tidak<= a and b

Tingkah laku akhir

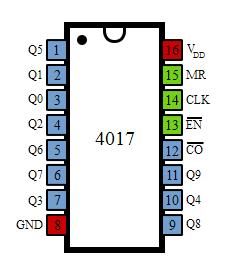

Nombor IC Setengah Adder

Pelaksanaan half adder dapat dilakukan melalui litar bersepadu logik digital CMOS berkelajuan tinggi seperti siri 74HCxx yang merangkumi SN74HC08 (7408) & SN74HC86 (7486).

Batasan Setengah Penambah

Sebab utama untuk memanggil penambah binari ini seperti Half Adders adalah, bahawa tidak ada julat untuk memasukkan bit bawa menggunakan bit sebelumnya. Jadi, ini adalah batasan utama HA yang pernah digunakan seperti penambah binari terutamanya dalam situasi masa nyata yang melibatkan penambahan beberapa bit. Jadi had ini dapat diatasi dengan menggunakan penambah penuh.

Penambah Penuh

Penambah ini sukar dilaksanakan jika dibandingkan dengan penambah separuh.

Diagram Fungsi Penambah Penuh

Perbezaan antara half-adder dan full-adder adalah bahawa full-adder mempunyai tiga input dan dua output, sedangkan half adder hanya memiliki dua input dan dua output. Dua input pertama adalah A dan B dan input ketiga adalah input input sebagai C-IN. Apabila logik penambah penuh dirancang, anda merangkai lapan daripadanya untuk membuat penambah lebar bait dan melampirkan bit pembawa dari satu penambah ke yang berikutnya.

Jadual Kebenaran FA

Hasil keluaran ditetapkan sebagai C-OUT dan output normal ditunjukkan sebagai S yang merupakan 'SUM'.

Dengan perkara di atas jadual kebenaran penambah penuh , pelaksanaan rangkaian penambah penuh dapat difahami dengan mudah. SUM ‘S’ dihasilkan dalam dua langkah:

- Dengan XORing input yang disediakan ‘A’ dan ‘B’

- Hasil A XOR B kemudian XORed dengan C-IN

Ini menghasilkan SUM dan C-OUT hanya berlaku apabila kedua-dua daripada tiga input TINGGI, maka C-OUT akan TINGGI. Oleh itu, kita dapat melaksanakan litar penambah penuh dengan bantuan dua litar separuh penambah. Pada mulanya, half adder akan digunakan untuk menambahkan A dan B untuk menghasilkan Sum separa dan logik penambah separuh kedua dapat digunakan untuk menambahkan C-IN ke Sum yang dihasilkan oleh penambah separuh pertama untuk mendapatkan output S akhir.

Sekiranya ada logik setengah penambah menghasilkan daya bawa, akan ada hasil keluaran. Jadi, C-OUT akan menjadi fungsi ATAU dari output Carry separuh tambah. Lihat pelaksanaan litar penambah penuh seperti di bawah.

Diagram Logik Penambah Penuh

Pelaksanaan gambarajah logik yang lebih besar adalah mungkin dengan logik penambah penuh di atas, simbol yang lebih sederhana kebanyakannya digunakan untuk mewakili operasi. Diberikan di bawah ini adalah gambaran skematik yang lebih mudah bagi penambah penuh satu bit.

Dengan jenis simbol ini, kita dapat menambahkan dua bit bersama-sama, membawa jarak dari susunan magnitud yang lebih rendah seterusnya, dan mengirim nilai ke susunan magnitud yang lebih tinggi berikutnya. Dalam komputer, untuk operasi multi-bit, setiap bit mesti diwakili oleh penambah penuh dan mesti ditambahkan secara serentak. Oleh itu, untuk menambahkan dua nombor 8-bit, anda memerlukan 8 penambah penuh yang boleh dibentuk dengan merangkaikan dua blok 4-bit.

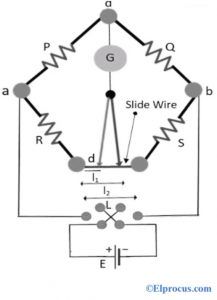

Separuh Penambah dan Penambah Penuh menggunakan K-Map

Malah jumlah dan output output untuk setengah penambah juga dapat diperoleh dengan kaedah peta Karnaugh (K-map). The separuh penambah dan ungkapan boolean penambah penuh boleh diperoleh melalui peta K. Jadi, peta K untuk penambah ini dibincangkan di bawah.

K-peta separuh tambah adalah

HA K-Peta

K-Map penambah penuh ialah

FA-Peta K

Ungkapan Logik SUM dan Carry

Ungkapan logik jumlah (S) dapat ditentukan berdasarkan input yang disebutkan dalam jadual.

= A'B'Cin + A 'B CCin' + A B'Cin '+ AB Cin

= Cin (A'B '+ AB) + Cin' (A'B + A B ')

= Cin EX-OR (A EX-ATAU B)

= (1,2,4,7)

Ekspresi logik carry (Cout) dapat ditentukan berdasarkan input yang disebutkan dalam jadual.

= A'B Cin + AB'Cin + AB Cin '+ ABCin

= AB + BCin + ACin

= (3, 5, 6, 7)

Dengan jadual kebenaran yang disebutkan di atas, hasilnya dapat diperoleh dan prosedurnya adalah:

Litar gabungan menggabungkan gerbang yang berbeza dalam litar di mana mereka boleh menjadi pengekod, penyahkod, multiplexer dan demultiplexer . Ciri-ciri litar kombinasi adalah seperti berikut.

- Keluaran pada bila-bila masa hanya berdasarkan pada tahap yang ada di terminal input.

- Ia tidak menggunakan memori. Keadaan input sebelumnya tidak memberi kesan pada keadaan litar sekarang.

- Ia dapat memiliki sejumlah input dan sejumlah output.

Pengekodan VHDL

Pengekodan VHDL untuk penambah penuh sertakan perkara berikut.

entiti full_add adalah

Pelabuhan (a: dalam STD_LOGIC

b: dalam STD_LOGIC

cin: dalam STD_LOGIC

jumlah: keluar STD_LOGIC

cout: keluar STD_LOGIC)

tamat penuh_add

Tingkah Laku Senibina full_add adalah

komponen ha adalah

Pelabuhan (a: dalam STD_LOGIC

b: dalam STD_LOGIC

sha: keluar STD_LOGIC

cha: keluar STD_LOGIC)

komponen akhir

isyarat s_s, c1, c2: STD_LOGIC

bermula

HA1: peta pelabuhan ha (a, b, s_s, c1)

HA2: peta pelabuhan ha (s_s, cin, sum, c2)

kos<=c1 or c2

Tingkah laku akhir

The perbezaan antara half adder dan full adder ialah separuh penambah menghasilkan hasil dan penambah penuh menggunakan separuh penambah untuk menghasilkan beberapa hasil lain. Begitu juga, sementara Penuh Penuh terdiri daripada dua Penambah Setengah, Penambah Penuh adalah blok sebenarnya yang kita gunakan untuk membuat litar aritmetik.

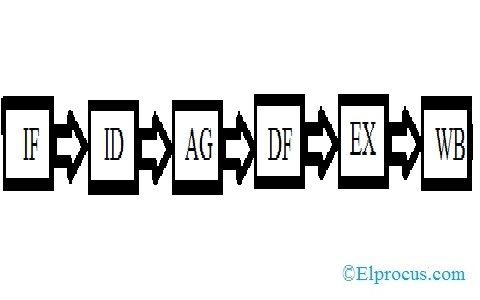

Carilah Penambah Lookahead

Dalam konsep litar penambah riak membawa, bit yang diperlukan untuk penambahan segera tersedia. Manakala setiap bahagian penambah perlu meluangkan waktunya untuk kedatangan bawaan dari blok penambah sebelumnya. Oleh kerana itu, memerlukan lebih banyak masa untuk menghasilkan SUM dan CARRY kerana setiap bahagian dalam litar menunggu kedatangan input.

Sebagai contoh, untuk memberikan output untuk blok ke-9, ia perlu menerima input dari blok n-1. Dan kelewatan ini juga disebut sebagai penangguhan penyebaran.

Untuk mengatasi kelewatan riak membawa adder, sebuah penambah carry-lookahead diperkenalkan. Di sini, dengan menggunakan perkakasan yang rumit, kelewatan penyebaran dapat diminimumkan. Gambar rajah di bawah menunjukkan penambah carry-lookahead menggunakan penambah penuh.

Bawa Lookahead Menggunakan Penambah Penuh

Jadual kebenaran dan persamaan output yang sesuai adalah

| KE | B | C | C + 1 | Keadaan |

| 0 | 0 | 0 | 0 | Tidak Membawa Menjana |

| 0 | 0 | 1 | 0 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 1 | Tidak Membawa Menyebarkan |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 1 | Bawa Menjana |

| 1 | 1 | 1 | 1 |

Persamaan penyebaran bawa adalah Pi = Ai XOR Bi dan hasil bawa adalah Gi = Ai * Bi. Dengan persamaan ini, persamaan jumlah dan bawa dapat ditunjukkan sebagai

SUM = Pi XOR Ci

Ci + 1 = Gi + Pi * Ci

Gi memberikan daya bawa hanya apabila kedua-dua input Ai dan Bi adalah 1 tanpa mempertimbangkan input dibawa. Pi berkaitan dengan penyebaran bawa dari Ci ke Ci + 1.

Perbezaan antara Half Adder dan Full Adder

The perbezaan antara jadual penambah separuh dan penambah penuh ditunjukkan di bawah.

| Separuh Penambah | Penambah Penuh |

| Half Adder (HA) adalah litar logik gabungan dan litar ini digunakan untuk menambahkan dua digit satu bit. | Penambah Penuh (FA) adalah litar gabungan dan litar ini digunakan untuk menambahkan tiga digit satu bit. |

| Di HA, setelah dibawa dihasilkan dari penambahan sebelumnya tidak dapat ditambahkan ke langkah berikutnya. | Di FA, setelah dibawa dihasilkan dari penambahan sebelumnya, maka dapat ditambahkan ke langkah berikutnya. |

| Setengah penambah merangkumi dua gerbang logik seperti gerbang AND dan gerbang EX-OR. | Penambah penuh merangkumi dua pintu EX-OR, dua pintu OR, dan dua pintu AND. |

| Bit input dalam separuh penambah adalah dua seperti A, B. | Bit input dalam penambah penuh adalah tiga seperti A, B & C-in |

| Separuh jumlah tambah dan persamaan bawa adalah S = a⊕b C = a * b | Ungkapan logik penambah penuh ialah S = a ⊕ b⊕Cin Cout = (a * b) + (Cin * (a⊕b)). |

| HA digunakan dalam komputer, kalkulator, peranti yang digunakan untuk pengukuran digital, dll. | FA digunakan dalam pemproses digital, penambahan bit ganda, dll. |

The perbezaan utama antara half adder dan full adder dibincangkan di bawah.

- Setengah penambah menghasilkan jumlah & bawa dengan menambahkan dua input binari sedangkan penambah penuh digunakan untuk menghasilkan jumlah & bawa dengan menambahkan tiga input binari. Kedua-dua senibina perkakasan separuh penambah dan penambah penuh tidak sama.

- Ciri utama yang membezakan HA & FA adalah bahawa di HA tidak ada kesepakatan untuk mempertimbangkan penambahan terakhir seperti inputnya. Tetapi, FA meletakkan lajur input tertentu seperti Cin untuk mempertimbangkan sedikit penambahan terakhir.

- Kedua-dua penambah akan menunjukkan perbezaan berdasarkan komponen yang digunakan dalam litar untuk pembinaannya. Penambah separuh (HA's) direka dengan gabungan dua gerbang logik seperti AND & EX-OR sedangkan FA direka dengan gabungan tiga pintu AND, dua XOR & satu ATAU.

- Pada dasarnya, HA beroperasi pada input 2-dua 1-bit, sedangkan FA beroperasi pada tiga input 1-bit. Setengah penambah digunakan dalam peranti elektronik yang berbeza untuk menilai penambahan sementara penambah penuh digunakan dalam pemproses digital untuk penambahan jangka panjang.

- Kesamaan dalam kedua-dua penambah ini adalah, kedua-dua HA & FA adalah litar digital gabungan sehingga, mereka tidak menggunakan elemen memori seperti litar berurutan. Litar ini penting untuk operasi aritmetik untuk memberikan penambahan nombor binari.

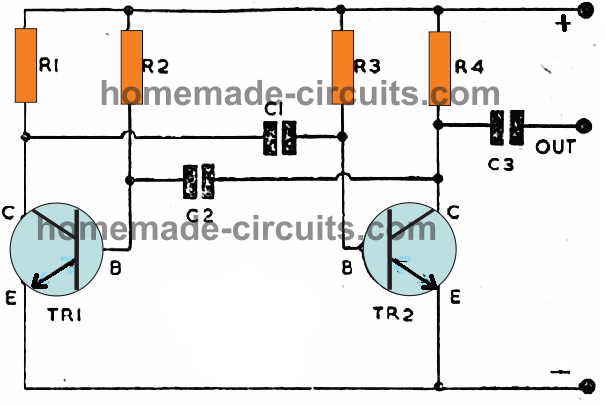

Pelaksanaan Penambah Penuh menggunakan Setengah Penambah

Pelaksanaan FA boleh dilakukan melalui dua setengah penambah yang dihubungkan secara logik. Gambarajah blok ini dapat ditunjukkan di bawah yang menceritakan hubungan FA menggunakan dua setengah penambah.

Jumlah dan persamaan bawa dari pengiraan sebelumnya adalah

S = A 'B' Cin + A 'BC' di + ABCin

Cout = AB + ACin + BCin

Jumlah persamaan boleh ditulis sebagai.

Cin (A’B ‘+ AB) + C‘ in (A’B + A B ’)

Jadi, Jumlah = Cin EX-OR (A EX-OR B)

Cin (A EX-OR B) + C'in (A EX-OR B)

= Cin EX-OR (A EX-ATAU B)

Cout boleh ditulis seperti berikut.

COUT = AB + ACin + BCin.

Cout = AB + + kekecewaan BCin (A + A)

= ABCin + AB + ACin + A 'B Cin

= AB (1 + Cin) + ACin + A 'B Cin

= A B + ACin + A 'B Cin

= AB + ACin (B + B ') + A' B Cin

= ABCin + AB + A'B Cin + A 'B Cin

= AB (Cin + 1) + A B Cin + A 'B Cin

= AB + AB 'Cin + A' B Cin

= AB + Cin (AB '+ A'B)

Oleh itu, COUT = AB + Cin (A EX-OR B)

Bergantung pada dua persamaan jumlah & bawa di atas, litar FA dapat dilaksanakan dengan bantuan dua HA & gerbang ATAU. Gambarajah litar penambah penuh dengan dua setengah penambah digambarkan di atas.

Penambah Penuh menggunakan Dua Penambah Separuh

Reka Bentuk Penambah Penuh dengan menggunakan NAND Gates

Gerbang NAND adalah salah satu jenis gerbang sejagat, yang digunakan untuk melaksanakan reka bentuk logik apa pun. Litar FA dengan rajah gerbang NAND ditunjukkan di bawah.

FA menggunakan NAND Gates

FA adalah penambah satu-bit yang mudah dan jika kita ingin melaksanakan penambahan n-bit, maka n tidak. FA satu bit mesti digunakan dalam format sambungan lata.

Kelebihan

The kelebihan half adder dan full adder sertakan perkara berikut.

- Tujuan utama penambah setengah adalah untuk menambah dua nombor bit tunggal

- Penambah penuh mempunyai keupayaan untuk menambah bawaan yang dihasilkan dari penambahan sebelumnya

- Dengan penambah penuh, litar penting seperti adder, multiplexer, dan banyak lagi boleh dilaksanakan

- Litar penambah penuh menggunakan kuasa minimum

- Kelebihan penambah penuh lebih dari setengah penambah adalah, penambah penuh digunakan untuk mengatasi kekurangan setengah penambah kerana separuh penambah digunakan terutamanya untuk menambahkan dua nombor 1-bit. Setengah penambah tidak menambah nilai tambah, jadi untuk mengatasi ini penambah penuh digunakan. Dalam Penambah penuh, penambahan tiga bit dapat dilakukan dan menghasilkan dua output.

- Reka bentuk penambah adalah mudah dan merupakan asas asas supaya penambahan satu bit dapat difahami dengan mudah.

- Penambah ini boleh ditukar menjadi setengah pengurang dengan menambahkan penyongsang.

- Dengan menggunakan penambah penuh, output yang tinggi dapat diperoleh.

- Kelajuan tinggi

- Sangat kuat untuk menyediakan penskalaan voltan

Kekurangan

The kekurangan separuh adder dan full adder sertakan perkara berikut.

- Sebagai tambahan, half adder tidak dapat digunakan sebelum membawa, jadi tidak dapat digunakan untuk menambahkan penambahan multi-bit.

- Untuk mengatasi kekurangan ini, FA perlu menambahkan tiga 1 bit.

- Setelah FA digunakan dalam bentuk rantai seperti RA (Ripple Adder), maka kemampuan pemacu output dapat dikurangkan.

Permohonan

Aplikasi half adder dan full adder merangkumi yang berikut.

- Penambahan bit binari boleh dilakukan dengan setengah penambah menggunakan ALU di dalam komputer kerana menggunakan penambah.

- Kombinasi separuh penambah boleh digunakan untuk merancang litar penambah penuh.

- Setengah penambah digunakan dalam kalkulator dan untuk mengukur alamat serta jadual

- Litar ini digunakan untuk menangani aplikasi yang berlainan dalam litar digital. Pada masa akan datang, ia memainkan peranan penting dalam elektronik digital.

- Litar FA digunakan sebagai elemen dalam banyak litar besar seperti Ripple Carry Adder. Penambah ini menambahkan bilangan bit secara serentak.

- FA digunakan dalam Unit Logik Aritmetik (ALU)

- FA digunakan dalam aplikasi berkaitan grafik seperti GPU (Unit Pemprosesan Grafik)

- Ini digunakan dalam litar pendaraban untuk melaksanakan Pendaraban Carryout.

- Di komputer, untuk menghasilkan alamat memori & untuk membina titik arah program ke arah arahan seterusnya, Unit Logik Aritmetik digunakan dengan menggunakan Penambah Penuh.

Oleh itu, setiap kali penambahan dua nombor binari dilakukan maka digit akan ditambahkan pada awalnya bit paling sedikit. Proses ini dapat dilakukan melalui setengah penambah kerana n / w termudah yang memungkinkan penambahan dua nombor 1-bit. Input dari penambah ini adalah digit binari sedangkan outputnya adalah jumlah (S) & bawaan (C).

Apabila bilangan digit disertakan, maka rangkaian HA digunakan hanya untuk menyambungkan digit paling sedikit, kerana HA tidak dapat menambahkan nombor bawa dari kelas sebelumnya. Penambah lengkap boleh didefinisikan sebagai asas semua peranti aritmetik digital. Ini digunakan untuk menambahkan tiga nombor 1 digit. Penambah ini merangkumi tiga input seperti A, B, dan Cin sedangkan outputnya adalah Sum dan Cout.

Konsep Berkaitan

The konsep yang berkaitan dengan half adder dan full adder tidak berpegang pada satu tujuan. Mereka memiliki penggunaan yang luas dalam banyak aplikasi dan beberapa yang terkait disebutkan:

- Setengah penambah dan nombor IC penambah penuh

- Pembangunan penambah 8-bit

- Apakah langkah berjaga-jaga setengah penambah?

- JAVA Applet dari Ripple Carry Adder

Oleh itu, ini semua berkaitan dengan teori half adder dan full adder bersama dengan jadual kebenaran dan gambarajah logik, reka bentuk penambah penuh menggunakan litar separuh penambah juga ditunjukkan. Sebilangan besar half adder dan full adder pdf dokumen tersedia untuk memberikan maklumat lanjut mengenai konsep-konsep ini. Lebih penting lagi untuk diketahui bagaimana penambah penuh 4-bit dilaksanakan ?