Artikel ini menerangkan mengenai penjanaan modulasi lebar nadi isyarat dengan kitaran tugas berubah pada FPGA menggunakan VHDL. PWM mempunyai frekuensi tetap dan voltan berubah. Artikel ini juga membincangkan Pengurus Jam Digital untuk mengurangkan frekuensi jam dengan mengurangkan kecenderungan isyarat jam. Frekuensi tetap digunakan untuk menghasilkan data input yang menghasilkan isyarat PWM menggunakan pembanding. Syarikat elektronik merancang perkakasan yang dikhaskan untuk produk mereka dengan standard dan protokolnya yang menjadikannya sukar bagi pengguna akhir untuk mengkonfigurasi semula perkakasan sesuai dengan keperluan mereka. Keperluan untuk perkakasan ini menyebabkan pertumbuhan segmen baru yang dapat dikonfigurasi oleh pelanggan litar bersepadu lapangan yang boleh diprogramkan yang disebut FPGA .

Modulasi Lebar Nadi (PWM)

Modulasi lebar nadi banyak digunakan dalam aplikasi komunikasi dan sistem kawalan . Modulasi lebar nadi dapat dihasilkan dengan menggunakan pendekatan yang berbeza dalam sistem kawalan. Di sini, dalam artikel ini, PWM dihasilkan menggunakan Bahasa Huraian Perkakasan (VHDL) dan dilaksanakan pada FPGA. Pelaksanaan PWM pada FPGA dapat memproses data lebih cepat dan arsitektur pengawal dapat dioptimumkan untuk ruang atau kecepatan.

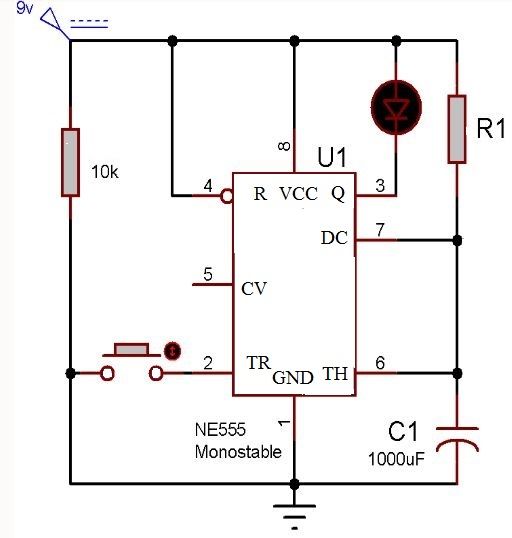

PWM adalah teknik untuk menyediakan logik ‘0’ dan logik ‘1’ untuk jangka masa yang terkawal. Ini adalah sumber isyarat yang melibatkan modulasi kitaran tugasnya untuk mengawal jumlah daya yang dihantar ke beban. Dalam PWM, jangka masa gelombang persegi tetap tetap dan masa di mana isyarat kekal TINGGI adalah berbeza-beza.

PWM menghasilkan denyutan pada outputnya sedemikian rupa sehingga nilai rata-rata TINGGI dan RENDAH sebanding dengan input PWM. Kitaran tugas isyarat boleh berbeza-beza. Isyarat PWM adalah gelombang persegi jangka masa tetap dengan pelbagai kitaran tugas. Maksudnya, frekuensi isyarat PWM adalah tetap, tetapi jangka masa isyarat tetap tinggi dan berbeza seperti yang ditunjukkan.

Isyarat PWM

VHDL

VHDL adalah bahasa, digunakan untuk menggambarkan tingkah laku reka bentuk litar digital . VHDL digunakan oleh industri dan akademik untuk tujuan simulasi litar digital. Reka bentuknya dapat disimulasikan dan diterjemahkan dalam bentuk yang sesuai untuk dilaksanakan dalam perkakasan.

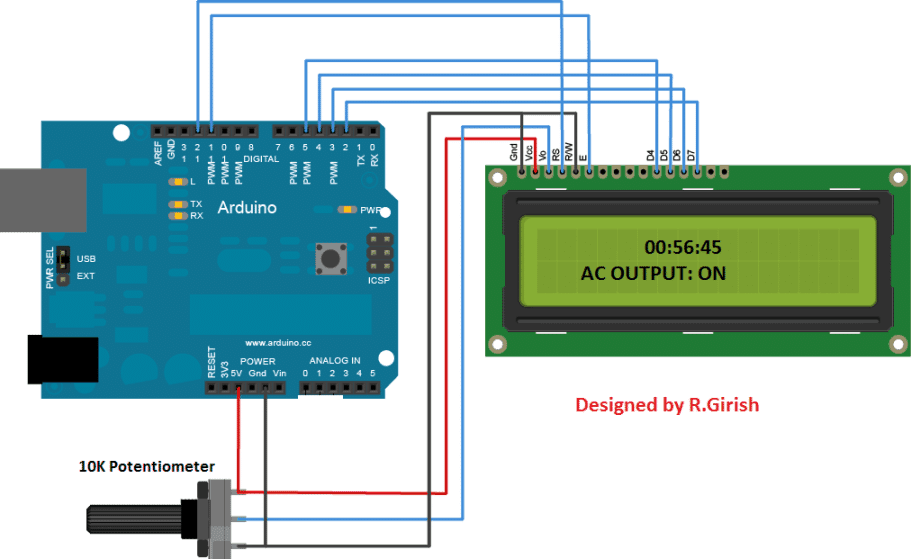

Senibina PWM

Untuk menghasilkan data input untuk menghasilkan PWM menggunakan pembilang berjalan bebas N-bit berkelajuan tinggi, yang outputnya dibandingkan dengan output daftar dan menyimpan kitaran tugas input yang diinginkan dengan bantuan pembanding. Pembanding output ditetapkan ke 1 apabila kedua-dua nilai ini sama. Output pembanding ini digunakan untuk mengatur kait RS. Isyarat limpahan dari kaunter digunakan untuk menetapkan semula kait RS. The keluaran selak RS memberikan output PWM yang diingini. Isyarat limpahan ini juga digunakan untuk memuat kitaran tugas N-bit baru dalam Daftar. PWM mempunyai frekuensi tetap dan voltan berubah. Nilai voltan ini berubah dari 0V hingga 5 V.

Isyarat PWM dengan kitaran tugas berubah

PWM asas menghasilkan isyarat, yang memberikan output PWM, memerlukan pembanding yang membandingkan antara dua nilai. Nilai pertama mewakili isyarat kuasa dua yang dihasilkan oleh pembilang bit N dan nilai kedua mewakili isyarat persegi yang mengandungi maklumat mengenai kitaran tugas. Kaunter menghasilkan isyarat beban setiap kali terdapat limpahan. Setelah isyarat beban menjadi aktif, daftar memuat nilai kitaran tugas yang baru. Isyarat beban digunakan untuk mengatur semula kait juga. Latch output adalah isyarat PWM. Ini berbeza dengan perubahan nilai kitaran tugas.

Apa itu FPGA?

FPGA adalah Field Array Gate Array. Ia adalah sejenis peranti yang banyak digunakan dalam litar elektronik. FPGA adalah peranti semikonduktor yang mengandungi blok logik dan litar interkoneksi. Ia dapat diprogramkan atau diprogram ulang ke fungsi yang diperlukan setelah pembuatan.

FPGA

Asas FPGA

Apabila papan litar dihasilkan dan jika ia mengandungi FPGA sebagai sebahagian daripadanya. Ini diprogramkan semasa proses pembuatan dan selanjutnya dapat diprogram ulang kemudian untuk membuat kemas kini atau membuat perubahan yang diperlukan. Ciri FPGA ini menjadikannya unik dari ASIC. Aplikasi Litar Bersepadu Khusus (ASIC) dibuat khas untuk tugas reka bentuk tertentu. Pada masa lalu FPGA digunakan untuk mengembangkan kelajuan rendah, kerumitan dan reka bentuk kelantangan, tetapi hari ini FPGA dengan mudah mendorong penghalang prestasi hingga 500MHz.

Dalam mikrokontroler, cip dirancang untuk pelanggan dan mereka harus menulis perisian dan menyusunnya ke file hex untuk dimuat ke mikrokontroler. Perisian ini dapat diganti dengan mudah kerana disimpan dalam memori kilat. Dalam FPGA, tidak ada pemproses untuk menjalankan perisian dan kami yang merancang litar. Kita boleh mengkonfigurasi FPGA semudah gerbang AND atau kompleks seperti pemproses multi-teras. Untuk membuat reka bentuk, kami menulis Bahasa Penerangan Perkakasan (HDL), yang terdiri daripada dua jenis - Verilog dan VHDL. Kemudian HDL disintesis ke dalam fail bit menggunakan BITGEN untuk mengkonfigurasi FPGA. FPGA menyimpan konfigurasi dalam RAM, yaitu konfigurasi hilang apabila tidak ada sambungan kuasa. Oleh itu, mereka mesti dikonfigurasi setiap kali kuasa dibekalkan.

Senibina FPGA

FPGA adalah cip silikon pasang siap yang dapat diprogramkan secara elektrik untuk melaksanakan reka bentuk digital. FPGA berasaskan memori statik pertama yang disebut SRAM digunakan untuk mengkonfigurasi logik dan interkoneksi menggunakan aliran bit konfigurasi. EPGA moden hari ini mengandungi kira-kira 3,30,000 blok logik dan sekitar 1,100 input dan output.

Senibina FPGA

Seni bina FPGA terdiri daripada tiga komponen utama

- Blok Logik yang Dapat Diprogramkan, yang melaksanakan fungsi logik

- Routing yang boleh diprogramkan (saling berkaitan), yang melaksanakan fungsi

- Blok I / O, yang digunakan untuk membuat sambungan off-chip

Aplikasi isyarat PWM

Isyarat PWM digunakan secara meluas untuk aplikasi kawalan. Seperti mengawal motor DC, injap kawalan, pam, hidraulik, dan lain-lain Berikut adalah beberapa aplikasi isyarat PWM.

- Sistem pemanasan dengan masa perlahan 10 hingga 100Hz atau lebih tinggi.

- Motor elektrik DC 5 hingga 10KHz

- Bekalan kuasa atau penguat audio 20 hingga 200 KHz.

Artikel ini adalah mengenai penjanaan isyarat PWM dengan kitaran tugas berubah menggunakan FPGA. Selanjutnya, untuk sebarang bantuan mengenai projek elektronik atau keraguan mengenai artikel ini, anda boleh menghubungi kami dengan memberi komen di bahagian komen yang diberikan di bawah.