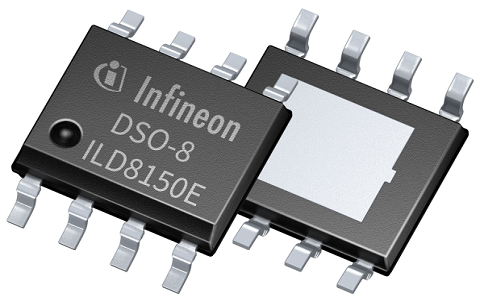

Dalam kehidupan seharian kita, kita menemui pelbagai jenis alat elektronik. Salah satu teknologi yang membawa revolusi dalam pengeluaran elektronik adalah ' Litar bersepadu '. Teknologi ini mengurangkan saiz produk elektronik dengan meningkatkan ketumpatan gerbang logik setiap cip. Hari ini kita mempunyai pelbagai jenis dan konfigurasi IC. Seperti yang kita amati di sekitar, kita dapati beberapa IC hanya dapat digunakan untuk satu aplikasi tertentu sementara beberapa IC dapat diprogram ulang dan digunakan untuk berbagai aplikasi. Jenis IC ini dinamakan ASIC. Tetapi bagaimana mereka berbeza? Bagaimana mungkin untuk memprogram semula mereka? Mengapa beberapa IC tidak dapat diprogramkan semula? Berharap untuk mencari jawapan kepada soalan-soalan ini.

Apa itu ASIC (Litar Bersepadu Khusus Aplikasi)?

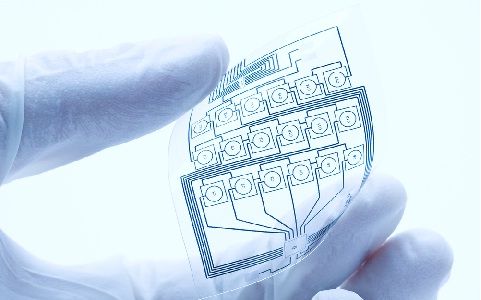

Borang penuh ASIC adalah Litar Bersepadu Khusus Aplikasi. Litar ini khusus aplikasi .i. IC yang dibuat khas untuk aplikasi tertentu. Ini biasanya dirancang dari peringkat akar berdasarkan keperluan aplikasi tertentu. Sebilangan asas contoh litar bersepadu khusus aplikasi adalah cip yang digunakan dalam mainan, cip yang digunakan untuk antara muka memori dan mikropemproses dll ... Cip ini hanya boleh digunakan untuk satu aplikasi yang dirancang. Agaknya, ini jenis IC hanya disukai untuk produk yang mempunyai jangka masa pengeluaran yang besar. Oleh kerana ASIC direka dari peringkat akar, ia mempunyai kos yang tinggi dan disyorkan hanya untuk pengeluaran dengan jumlah yang tinggi.

Kelebihan utama ASIC adalah mengurangkan saiz cip kerana sebilangan besar unit fungsian litar dibina melalui satu cip. ASIC moden secara amnya merangkumi 32-bit mikropemproses , blok memori, litar rangkaian dan lain-lain ... ASIC jenis ini dikenali sebagai Sistem pada Cip . Dengan perkembangan teknologi pembuatan dan peningkatan penyelidikan dalam kaedah reka bentuk, ASIC dengan tahap penyesuaian yang berbeza dikembangkan.

Jenis-jenis ASIC

ASIC dikategorikan berdasarkan jumlah penyesuaian yang dibenarkan oleh pengaturcara pada cip.

Jenis ASIC

Adat Penuh

Dalam jenis reka bentuk ini, semua sel logik dibuat khusus untuk aplikasi tertentu. pereka harus membuat sel logik khas untuk litar. Semua lapisan topeng untuk interkoneksi disesuaikan. Oleh itu, pengaturcara tidak dapat mengubah interkoneksi cip dan semasa memprogram, dia harus mengetahui susunan litar.

Salah satu contoh terbaik ASIC adat penuh ialah mikropemproses. Jenis penyesuaian ini membolehkan pereka membina pelbagai litar analog, sel memori yang dioptimumkan, atau struktur mekanikal pada satu IC. ASIC ini mahal dan sangat memakan masa untuk pembuatan dan reka bentuk. Masa yang diambil untuk merancang IC ini adalah sekitar lapan minggu.

Ini biasanya bertujuan untuk aplikasi peringkat tinggi. Prestasi maksimum, kawasan minimum dan tahap fleksibiliti tertinggi adalah ciri utama reka bentuk khas penuh. Akhirnya, risikonya tinggi dalam reka bentuk kerana sel logik, perintang dan lain-lain ... elemen litar yang digunakan tidak diuji.

Separa Adat

Dalam reka bentuk jenis ini sel logik diambil dari pustaka standard .i.e. mereka tidak buatan tangan seperti dalam reka bentuk khas Penuh. Sebilangan topeng disesuaikan sementara yang lain diambil dari perpustakaan yang telah dirancang sebelumnya. Berdasarkan jenis sel logik yang diambil dari perpustakaan dan jumlah penyesuaian yang dibenarkan untuk saling menghubungkan ASIC ini dibahagikan kepada dua jenis - ASIC berasaskan sel standard dan ASIC berasaskan Array Gate.

1). ASIC berasaskan sel standard

Untuk mengetahui IC ini terlebih dahulu mari kita memahami apa maksud perpustakaan sel standard. Sebilangan sel logik seperti DAN gerbang, ATAU gerbang , multiplexer, selipar dirancang oleh pereka menggunakan konfigurasi yang berbeza, diseragamkan dan disimpan dalam bentuk perpustakaan. Koleksi ini dikenali sebagai perpustakaan sel standard.

ASIC berasaskan sel standard

Dalam sel standard, sel logik ASIC dari perpustakaan standard ini digunakan. Pada kawasan sel standard ASIC chip atau blok fleksibel terdiri daripada sel standard yang disusun dalam bentuk baris. Seiring dengan blok fleksibel ini sel-sel mega seperti mikrokontroler atau bahkan mikropemproses digunakan pada cip. Sel mega ini juga dikenal sebagai fungsi Mega, makro tahap sistem, blok tetap, blok standard berfungsi.

Rajah di atas mewakili ASIC sel piawai dengan luas sel standard tunggal dan empat blok tetap. Lapisan topeng disesuaikan. Di sini pereka boleh meletakkan sel standard di mana sahaja di bahagian mati. Ini juga dikenali sebagai C-BIC.

2). ASIC Berasaskan Gerbang Array

Jenis ASIC separa adat ini telah ditentukan sebelumnya transistor pada wafer silikon .i.e. pereka tidak boleh mengubah penempatan transistor yang ada pada die. Susunan pangkalan adalah corak yang ditentukan dari array gerbang dan sel asas adalah sel berulang terkecil dari array asas.

Pereka hanya mempunyai tanggungjawab untuk menukar interkoneksi antara transistor menggunakan beberapa lapisan logam pertama dari die. Pereka memilih dari perpustakaan array gerbang. Ini sering disebut sebagai Masked Gate Array. Gate Array Based ASIC terdiri daripada tiga jenis. Mereka adalah Channeled Gate Array, Channel array array array dan array gerbang berstruktur.

a). Array Gerbang Saluran

Dalam susunan gerbang jenis ini, ruang pendawaian ditinggalkan di antara barisan transistor. Ini serupa dengan CBIC kerana ruang yang tersisa untuk saling menghubungkan antara blok tetapi dalam baris sel susunan gerbang disalurkan tetap tinggi sedangkan di CBIC ruang ini dapat disesuaikan.

Array Gate yang disalurkan

Beberapa ciri utama array gerbang ini adalah - array gerbang ini menggunakan ruang yang telah ditentukan di antara baris untuk sambungan. Masa pembuatan adalah dua hari hingga dua minggu.

b). Array Gerbang Kurang Saluran

Tidak ada ruang kosong yang tersisa untuk merutekan antara baris sel seperti yang terlihat dalam array gerbang yang disalurkan. Di sini routing dilakukan dari atas sel array gerbang kerana kita dapat menyesuaikan hubungan antara logam 1 dan transistor. Untuk penghalaan, kami membiarkan transistor terbaring di jalan penghalaan yang tidak digunakan. Masa pembuatan adalah sekitar dua minggu.

Array Gerbang Kurang Saluran

c). Array Pintu Berstruktur

Susunan gerbang jenis ini mempunyai blok tertanam bersama dengan barisan gerbang seperti yang dilihat di atas. Susunan gerbang berstruktur mempunyai kecekapan luas CBIC yang lebih tinggi. Seperti susunan gerbang bertopeng, ini mempunyai kos yang lebih rendah dan pemulihan lebih cepat. Di sini ukuran tetap fungsi tertanam menimbulkan batasan pada susunan gerbang berstruktur. Sebagai contoh, adakah array gerbang ini mengandungi kawasan yang dikhaskan untuk pengawal bit 32k tetapi jika dalam aplikasi kita hanya memerlukan kawasan untuk pengawal bit 16k, maka kawasan yang tinggal akan sia-sia. Semua susunan gerbang mempunyai masa pemulihan dari dua hari hingga dua minggu dan semua mempunyai interkoneksi yang disesuaikan.

Array Pintu Berstruktur

ASIC yang boleh diprogramkan

Terdapat dua jenis ASIC yang dapat diprogramkan. Mereka adalah PLD dan FPGA

PLD (Peranti Logik yang Boleh Diprogramkan)

Ini adalah sel standard yang sedia ada. Kami dapat memprogram PLD untuk menyesuaikan sebagian aplikasi, sehingga mereka dianggap ASIC. Kita boleh menggunakan kaedah dan perisian yang berbeza untuk memprogram PLD. Ini mengandungi matriks sel logik biasa biasanya logik array yang dapat diprogramkan bersama dengan sandal jepit atau selak. Di sini interkoneksi hadir sebagai satu blok besar tunggal.

PROM adalah contoh biasa IC ini. EPROM menggunakan transistor MOS sebagai interkoneksi jadi dengan menggunakan voltan tinggi kita dapat memprogramkannya. PLD tidak mempunyai sel logik atau saling berhubung. Ini mempunyai perubahan reka bentuk yang cepat.

Peranti Logik yang Boleh Diprogramkan

FPGAs (Array Gerbang Programmable Lapangan)

Di mana PLD mempunyai logik array yang dapat diprogram sebagai sel logik FPGA mempunyai susunan pintu gerbang seperti. PLD lebih kecil dan kurang kompleks daripada FPGA. Kerana fleksibiliti dan ciri-cirinya, FPGA menggantikan TTL dalam sistem mikroelektronik. Pemulihan reka bentuk hanya beberapa jam.

Array Gerbang diprogramkan di lapangan

Inti terdiri daripada sel logik asas yang dapat diprogramkan yang dapat melakukan kedua-duanya gabungan dan logik berurutan . Kita boleh memprogram sel logik dan saling berhubung menggunakan beberapa kaedah. Sel logik asas dikelilingi oleh matriks interkoneksi yang dapat diprogram dan inti dikelilingi oleh sel I / O yang dapat diprogramkan.

FPGA biasanya terdiri daripada blok logik yang boleh dikonfigurasi, blok I / O yang dapat dikonfigurasi, interkoneksi yang dapat diprogramkan, litar jam, ALU, memori, penyahkod.

Kami telah melihat pelbagai jenis ASIC yang ada. Sekarang mari kita fahami bila semua penyesuaian dan interkoneksi ini dilakukan semasa pembuatan.

Aliran Rekabentuk Litar Bersepadu Khusus (ASIC) Aplikasi

Merancang ASIC dilakukan mengikut langkah demi langkah. Susunan langkah ini dikenali sebagai Reka Bentuk ASIC Aliran. Langkah-langkah aliran reka bentuk diberikan dalam carta alir di bawah.

Aliran Reka Bentuk ASIC

Kemasukan Reka Bentuk: Pada langkah ini, seni bina mikro reka bentuk dilaksanakan menggunakan bahasa deskripsi perkakasan seperti VHDL, Verilog dan System Verilog.

Sintesis Logik: Pada langkah ini, senarai sel logik yang akan digunakan, jenis interkoneksi dan semua bahagian lain yang diperlukan untuk aplikasi disediakan menggunakan HDL.

Pembahagian Sistem: Pada langkah ini, kami membahagikan die yang berukuran besar menjadi kepingan berukuran ASIC.

Simulasi Pra-Layout: Pada langkah ini, ujian simulasi dilakukan untuk memeriksa sama ada reka bentuk mengandungi sebarang kesalahan.

Perancangan Lantai: Pada langkah ini blok netlist disusun pada chip.

Penempatan: Pada tahap ini lokasi sel di dalam blok ditentukan.

Laluan: Pada langkah ini, hubungan dibuat antara blok dan sel. Pengekstrakan: Pada langkah ini, kita menentukan sifat elektrik seperti nilai rintangan dan nilai kapasitansi interkoneksi.

Simulasi Pasca Tata Letak: Sebelum penyerahan model untuk pembuatan simulasi ini dilakukan untuk memeriksa apakah sistem berfungsi dengan baik bersama dengan beban interkoneksi.

Contoh ASIC

Setelah mengetahui pelbagai ciri ASIC sekarang mari kita lihat beberapa contoh ASIC.

ASIC berasaskan sel standard: LCB 300k, 500k dari LSI Logic Company, SIG1, 2, 3 keluarga dari ABB Hafo Inc., GCS90K dari GCS Plessey.

Produk Gate Array: AUA20K dari Harris Semiconductor, SCX6Bxx dari National Semiconductor, keluarga TGC / TEC dari Texas Instruments.

Produk PLD: Keluarga PAL Peranti Mikro Lanjutan, keluarga GAL dari Philips Semiconductors, XC7300 dan EPLD dari XILINX.

Produk FPGA: XC2000, XC3000, XC4000, XC5000 siri dari XILINX, pASIC1 QuickLogic, MAX5000 dari Altera.

Aplikasi ASIC

Keunikan ASIC telah merevolusikan cara pembuatan elektronik. Ini mengurangkan ukuran mati sambil meningkatkan ketumpatan gerbang logik setiap cip. ASIC biasanya disukai untuk aplikasi peringkat tinggi. Cip ASIC digunakan sebagai teras IP untuk satelit, pembuatan ROM, Pengawal mikro dan pelbagai jenis aplikasi dalam sektor perubatan dan penyelidikan. Salah satu aplikasi tren ASIC ialah BITCOIN MINER.

Pelombong Bitcoin

Perlombongan cryptocurrency memerlukan perkakasan kuasa dan kelajuan tinggi yang lebih besar. CPU tujuan umum tidak dapat menyediakan kapasiti pengkomputeran yang lebih tinggi pada kelajuan tinggi. Pelombong bitcoin ASIC adalah cip yang dibina pada papan induk yang direka khas dan bekalan kuasa , dibina menjadi satu unit. Ini adalah perkakasan yang dirancang dengan sengaja hingga ke tahap cip untuk perlombongan bitcoin. Unit-unit ini dapat menjalankan algoritma cryptocurrency tunggal. Untuk jenis cryptocurrency yang berlainan, kami memerlukan pelombong lain.

Kelebihan & Kekurangan ASIC

The kelebihan ASIC sertakan perkara berikut.

- ASIC yang bersaiz kecil menjadikannya pilihan tinggi untuk sistem yang lebih besar dan canggih.

- Oleh kerana sebilangan besar litar dibina di atas satu cip, ini menyebabkan aplikasi berkelajuan tinggi.

- ASIC mempunyai penggunaan kuasa yang rendah.

- Oleh kerana ia adalah sistem pada cip, litar hadir berdampingan. Oleh itu, penghalaan yang sangat minimum diperlukan untuk menghubungkan pelbagai litar.

- ASIC tidak mempunyai masalah masa dan konfigurasi pasca pengeluaran.

The keburukan ASIC sertakan perkara berikut.

- Kerana ini adalah cip yang disesuaikan, mereka memberikan fleksibiliti yang rendah untuk pengaturcaraan.

- Oleh kerana kerepek ini mesti dirancang dari peringkat akar, kosnya seunit tinggi.

- ASIC mempunyai masa yang lebih besar untuk margin pasaran.

ASIC vs FPGA

Perbezaan antara ASIC dan FPGA merangkumi yang berikut.

ASIC | FPGA |

| Tidak boleh diprogramkan semula | Boleh diprogramkan semula |

| Lebih disukai untuk pengeluaran dengan jumlah tinggi | Lebih disukai untuk pengeluaran dengan jumlah yang rendah |

| Ini adalah Aplikasi Khusus | Digunakan sebagai prototaip sistem |

| Tenaga Cekap memerlukan tenaga yang lebih sedikit | Kurang tenaga memerlukan lebih banyak tenaga |

| Ini adalah litar tetap yang tidak dapat ditingkatkan dari semasa ke semasa. | Sangat sesuai untuk aplikasi di mana litar mesti ditingkatkan dari semasa ke semasa seperti cip telefon bimbit, stesen pangkalan dll |

Oleh itu, ini adalah mengenai gambaran keseluruhan Litar Bersepadu Khusus Aplikasi . Penemuan ASIC telah menyebabkan perubahan besar dalam cara penggunaan elektronik. Kami menggunakan ASIC dalam kehidupan seharian dalam bentuk pelbagai aplikasi. Aplikasi ASIC mana yang pernah anda temui? Jenis ASIC yang pernah anda bekerjasama?