Dua jenis FET utama yang ada sekarang adalah: JFET dan MOSFET.

MOSFET boleh dikelaskan lebih lanjut ke dalam jenis penipisan dan jenis penambahbaikan. Kedua-dua jenis ini menentukan kaedah operasi asas MOSFET, sementara istilah MOSFET itu sendiri adalah singkatan transistor kesan medan-oksida-semikonduktor-medan.

Oleh kerana kedua-dua jenis mempunyai ciri kerja yang berbeza, kami akan menilai masing-masing secara berasingan dalam artikel yang berbeza.

Perbezaan antara Peningkatan dan Penipisan MOSFET

Pada dasarnya, tidak seperti peningkatan MOSFET, MOSFET penipisan berada dalam keadaan aktif walaupun terdapat 0 V melintasi terminal gerbang ke sumber (VGS).

Untuk peningkatan MOSFET, voltan pintu ke sumber (VGS) mesti berada di atas voltan ambang pintu ke sumbernya (VGS (th)) untuk menjadikannya berkelakuan .

Walau bagaimanapun, untuk MOSFET penipisan saluran-N, nilai VGS (th) di atas 0 V. Ini bermakna bahawa walaupun VGS = 0 V, MOSFET penipisan dapat mengalirkan arus. Untuk mematikannya, VGS penipisan MOSFET perlu dikurangkan di bawah VGS (th) (negatif).

Dalam artikel ini kita akan membincangkan jenis kekurangan MOSFET, yang dikatakan mempunyai ciri-ciri yang sepadan dengan JFET. Persamaannya adalah antara pemotongan dan ketepuan berhampiran IDSS.

Pembinaan Asas

Rajah 5.23 menunjukkan struktur dalaman asas MOSFET jenis penipisan saluran-n.

Kita dapat menemui sekumpulan bahan jenis p yang dibuat menggunakan pangkalan silikon. Blok ini dipanggil substrat.

Substrat adalah asas atau asas di mana MOSFET dibina. Bagi sebilangan MOSFET, ia dihubungkan secara dalaman dengan terminal 'sumber'. Juga, banyak peranti menawarkan output tambahan dalam bentuk SS, yang menampilkan MOSFET 4-terminal, seperti yang dinyatakan dalam Gambar.5.23

Saluran saliran dan sumber dihubungkan melalui kontak konduktif ke lokasi n-doped, dan dipasang melalui saluran n, seperti yang ditunjukkan dalam gambar yang sama.

Pintu gerbang juga dihubungkan ke lapisan logam, walaupun terlindung dari saluran n melalui lapisan halus silikon dioksida (SiOdua).

SiOduamempunyai bentuk sifat penebat yang unik yang disebut dielektrik yang mewujudkan medan elektrik yang bertentangan dalam dirinya sebagai tindak balas terhadap medan elektrik yang digunakan secara luaran.

Menjadi lapisan penebat, bahan SiOduamenawarkan maklumat penting berikut kepada kami:

Pengasingan lengkap dikembangkan antara terminal gerbang dan saluran mosfet dengan bahan ini.

Lebih-lebih lagi, ini kerana SiOdua, gerbang mosfet mampu menampilkan tahap impedans input yang sangat tinggi.

Oleh kerana harta impedans input tinggi yang penting ini, arus gerbang IGhampir tidak ada amp untuk konfigurasi MOSFET yang bias dc.

Operasi dan Karakteristik Asas

Seperti yang dapat dilihat pada Gambar.5.24, pintu masuk ke voltan sumber telah dikonfigurasi pada nol volt dengan menghubungkan kedua-dua terminal bersama-sama, sementara voltan VDSdigunakan di terminal longkang dan sumber.

Dengan tetapan di atas, bahagian longkang membentuk potensi positif oleh elektron bebas saluran n, bersama dengan arus yang setara melalui saluran JFET. Juga, arus V yang dihasilkanGS= 0V masih dikenali sebagai IDSS, seperti yang diberikan pada Gambar 5.25

Kita dapat melihat bahawa dalam Gambar.5.26 voltan sumber gerbang VGSdiberi potensi negatif dalam bentuk -1V.

Potensi negatif ini cuba memaksa elektron ke arah substrat saluran-p (kerana cas menolak), dan menarik lubang dari substrat saluran-p (kerana cas yang berlawanan menarik).

Bergantung pada seberapa besar bias negatif V iniGSadalah, pengumpulan semula lubang dan elektron berlaku yang mengakibatkan pengurangan elektron bebas di saluran-n yang tersedia untuk pengaliran. Tahap bias negatif yang lebih tinggi menyebabkan kadar pengumpulan semula yang lebih tinggi.

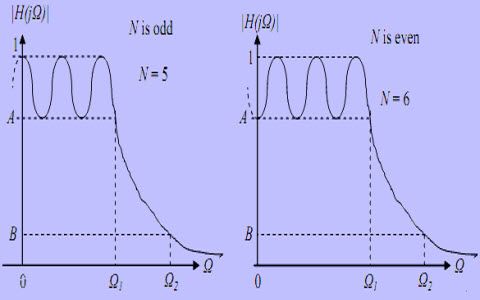

Arus saliran akibatnya berkurang apabila keadaan bias negatif di atas meningkat, yang terbukti dalam Gambar.5.25 untuk VGStahap VGS= -1, -2 dan seterusnya, sehingga tanda cubit -6V.

Arus pengaliran sebagai hasilnya bersama dengan plot kurva pemindahan berjalan sama seperti aliran a JFET.

Sekarang, untuk V positifGSnilai, pintu positif akan menarik lebihan elektron (pembawa bebas) dari substrat jenis-p, kerana arus kebocoran terbalik. Ini akan mewujudkan pembawa segar melalui pertembungan yang terhasil di zarah pecutan.

Oleh kerana voltan pintu-ke-sumber cenderung meningkat pada kadar positif, arus pengaliran menunjukkan peningkatan yang cepat, seperti yang dibuktikan dalam Rajah.5.25 dengan alasan yang sama seperti yang dibincangkan di atas.

Jurang berkembang antara lengkung VGS= 0V dan VGS= +1 menunjukkan dengan jelas jumlah kenaikan arus kerana variasi V - 1GS

Oleh kerana kenaikan arus pengaliran yang cepat, kita mesti berhati-hati dengan penilaian arus maksimum, jika tidak, ia boleh melepasi had voltan pintu positif.

Sebagai contoh, untuk jenis peranti yang digambarkan dalam Gambar.5.25, menggunakan VGS= + 4V akan menyebabkan arus pengaliran meningkat pada 22.2 mA, yang mungkin melintasi had kerosakan maksimum (arus) peranti.

Keadaan di atas menunjukkan bahawa penggunaan voltan pintu-ke-sumber positif menghasilkan kesan yang lebih baik terhadap kuantiti pembawa bebas di saluran, berbanding ketika VGS= 0V.

Inilah sebabnya mengapa kawasan voltan gerbang positif pada ciri longkang atau pemindahan umumnya dikenali sebagai wilayah peningkatan . Kawasan ini terletak di antara tahap pemotongan dan tahap tepu IDSSatau kawasan penipisan.

Menyelesaikan Masalah Contoh

Kelebihan dan Aplikasi

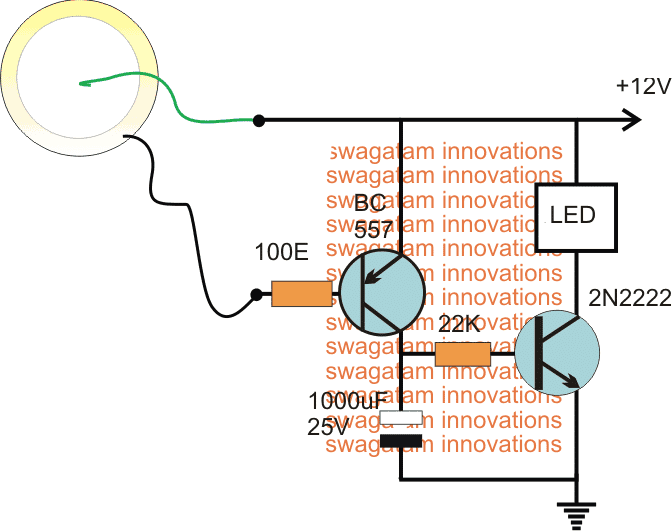

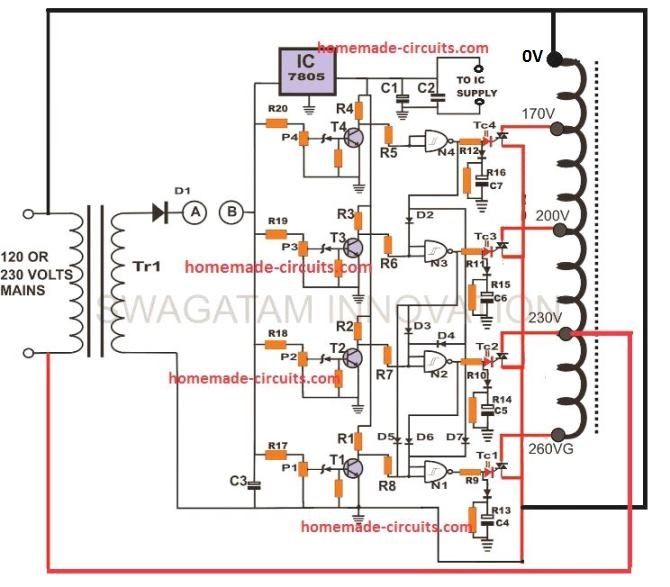

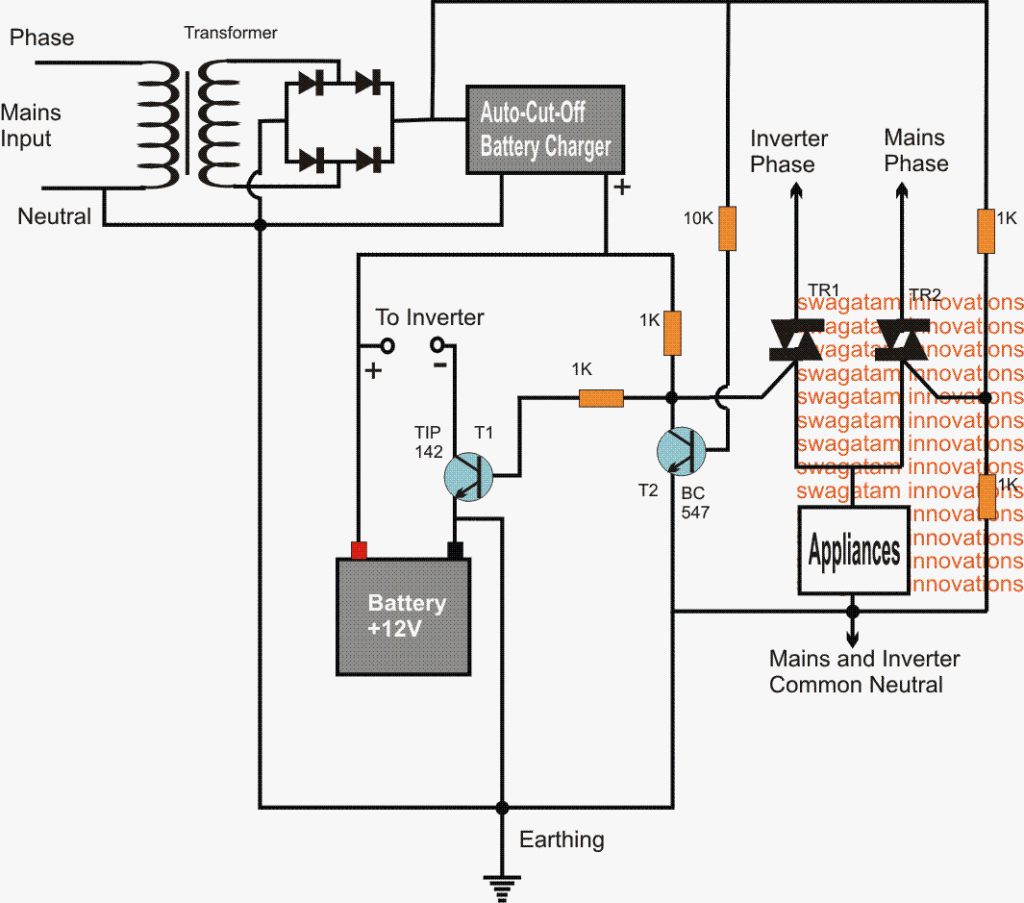

Berbeza dengan MOSFET mod peningkatan, di mana kita mendapati arus longkang turun menjadi sifar sebagai tindak balas terhadap voltan pintu-ke-sumber sifar, mod FET penipisan moden mempunyai arus yang ketara dengan voltan sifar gerbang. Tepatnya, rintangan saliran ke sumber biasanya 100 Ohm dalam voltan sifar.

Seperti yang ditunjukkan dalam grafik di atas, rds ON-resistance(di)vs jarak isyarat analog kelihatan seperti tindak balas yang hampir rata. Karakteristik ini, bersamaan dengan tahap kapasitansi rendah dari peranti jenis penipisan canggih ini, memungkinkannya menjadi ideal khusus sebagai suis analog untuk aplikasi pertukaran audio dan video.

Atribut mod kekurangan-normal MOSFET 'normal-on' membolehkan peranti ini sangat sesuai untuk pengatur arus FET tunggal.

Satu litar contoh seperti itu dapat dilihat pada gambar berikut.

Nilai Rs dapat ditentukan dengan menggunakan formula:

Rs= VGSmati[1 - (SayaD/ SayaDSS)1/2] / SayaD

di mana SayaD adalah jumlah arus terkawal yang diperlukan pada output.

Kelebihan utama MOSFET mod penipisan dalam aplikasi sumber semasa adalah kapasitansi pengaliran minimum mereka, yang menjadikannya sesuai untuk aplikasi bias dalam kebocoran input rendah, litar berkelajuan sederhana (> 50 V / us).

Rajah di bawah menunjukkan arus hadapan perbezaan rendah input-kebocoran menggunakan fungsi FET kebocoran rendah berganda.

Secara umum, kedua-dua sisi JFET akan berat sebelah pada ID = 500 uA. Oleh itu, arus yang dapat diperoleh untuk mengecas pampasan dan kapasiti sesat menjadi terhad kepada 2ID atau, dalam kes seperti ini, 1.0 mA. Ciri-ciri yang sesuai JFET terbukti produksi dan terjamin pada lembar data.

Cs melambangkan kapasitansi output dari sumber arus tahap 'ekor' input. Kapasitansi ini sangat penting dalam penguat bukan pembalik, kerana fakta bahawa tahap input mengalami pertukaran isyarat yang signifikan di seluruh rangkaian ini, dan arus pengecasan dalam Cs mungkin besar. Sekiranya sumber arus normal digunakan, kapasitansi ekor ini dapat dipertanggungjawabkan untuk kemerosotan kecepatan penurunan yang ketara pada litar non-pembalik (dibandingkan dengan aplikasi pembalik, di mana arus pengisian dalam C cenderung minimum).

Penurunan kadar sww dapat dinyatakan sebagai:

1 / 1+ (Cs / Sc)

Selagi Cs lebih rendah daripada Cc (kapasitor pampasan), hampir tidak mungkin terdapat variasi pada kadar slew. Bekerja dengan DMOS FET, Cs boleh menjadi sekitar 2 pF. Strategi ini menghasilkan peningkatan yang sangat besar dalam tahap penurunan. Di mana defisit arus lebih tinggi dari 1 hingga 5 mA diperlukan, peranti ini dapat diturunkan ke mod peningkatan untuk menghasilkan sebanyak 20 mA untuk VGS maksimum +2.5 V, dengan kapasitansi output minimum terus menjadi aspek penting.

Aplikasi seterusnya di bawah menunjukkan rangkaian sumber arus peningkatan yang betul.

Suis analog 'biasanya -on' dapat dibina untuk keperluan di mana keadaan standard menjadi perlu semasa kegagalan voltan bekalan, misalnya dalam alat ujian automatik atau untuk memastikan permulaan litar logik pada suis ON.

Voltan ambang negatif peranti yang dikurangkan menawarkan prasyarat pemacu asas dan izin bekerja dengan voltan minimum.

Litar di bawah menunjukkan faktor bias biasa untuk sebarang suis analog DMOS mod penipisan.

Untuk menyebabkan peranti dimatikan, voltan negatif diperlukan di pintu pagar. Setelah itu, daya tahan dapat dikurangkan ketika FET ditingkatkan dengan menggunakan voltan gerbang positif, yang memungkinkannya secara khusus di wilayah mod peningkatan bersama dengan kawasan mod-penipisan.

Tindak balas ini dapat dilihat dalam grafik berikut.

Kenaikan frekuensi tinggi unit, bersama dengan nilai kapasitansinya yang rendah, memberikan peningkatan 'angka prestasi'. Ini benar-benar elemen penting dalam penguatan VHF dan UHF, yang menentukan produk lebar jalur keuntungan (GBW) FET, yang dapat digambarkan sebagai:

GBW = gfs / 2 Pi (Cdalam+ Ckeluar)

p-Saluran Penipisan-Jenis MOSFET

Pembinaan MOSFET jenis penipisan saluran-p adalah kebalikan dari versi saluran-n yang ditunjukkan dalam Rajah 5.23. Maksudnya, substrat sekarang mengambil bentuk tipe-n dan saluran menjadi tipe-p, seperti yang dapat dilihat pada Gambar.5.28a di bawah.

Pengenalpastian terminal tidak berubah, tetapi voltan dan kutub arus terbalik, seperti yang ditunjukkan dalam rajah yang sama. Ciri pembuangan akan sama persis seperti yang digambarkan pada Gambar.55, kecuali VDStanda yang mana dalam kes ini akan mendapat nilai negatif.

Arus saliran IDmenunjukkan kekutuban positif dalam kes ini juga, itu kerana kita sudah membalikkan arahnya. VGSmenunjukkan kekutuban yang berlawanan, yang dapat dimengerti, seperti yang ditunjukkan pada Gambar.5.28c.

Kerana VGSditerbalikkan menghasilkan gambar cermin untuk ciri-ciri pemindahan seperti yang ditunjukkan pada Gambar 5,28b.

Maknanya, arus longkang meningkat pada V positifGSrantau dari titik pemotongan di VGS= Vp sehingga sayaDSS, maka ia terus meningkat sebagai nilai negatif VGSnaik.

Simbol

Tanda-tanda grafik untuk MOSFET jenis penipisan saluran n dan p dapat dilihat pada Gambar 5.29 di atas.

Perhatikan cara simbol yang dipilih bertujuan untuk mewakili struktur sebenar peranti.

Ketiadaan interkoneksi langsung (kerana penebat pintu) antara pintu dan saluran dilambangkan oleh jurang antara pintu gerbang dan terminal simbol yang berbeza.

Garis menegak yang mewakili saluran terpasang antara saluran dan sumber dan 'dipegang' oleh substrat.

Dua kumpulan simbol disediakan pada gambar di atas untuk setiap jenis saluran untuk menyoroti kenyataan bahawa dalam beberapa peranti substrat boleh diakses secara luaran sementara yang lain ini tidak dapat dilihat.

MOSFET (Jenis Peningkatan)

Walaupun jenis penipisan dan jenis peningkatan MOSFET kelihatan serupa dengan struktur dalaman dan mod fungsinya, ciri-cirinya mungkin agak berbeza.

Perbezaan utama adalah arus pengaliran yang bergantung pada tahap voltan pintu-ke-sumber tertentu untuk tindakan pemotongan.

Tepatnya, MOSFET jenis peningkatan saluran-n dapat berfungsi dengan voltan gerbang / sumber positif, dan bukannya rangkaian potensi negatif yang biasanya dapat mempengaruhi MOSFET jenis penipisan.

Pembinaan Asas

Anda boleh memvisualisasikan MOSFET jenis peningkatan saluran-n berikut

Rajah 5.31.

Bahagian bahan jenis-p dibuat melalui pangkalan silikon, dan seperti yang dipelajari sebelum ia disebut sebagai substrat.

Substrat ini pada beberapa kesempatan terpasang secara internal dengan pin sumber dalam MOSFET jenis penipisan, sementara dalam beberapa keadaan ia diakhiri sebagai petunjuk keempat untuk memungkinkan kawalan luaran dari tingkat potensinya.

Terminal sumber dan saliran seperti biasa digabungkan menggunakan kenalan logam ke kawasan n-doped.

Walau bagaimanapun, mungkin penting untuk membayangkan bahawa dalam Gambar 5.31 saluran antara dua kawasan n-doped hilang.

Ini mungkin dianggap sebagai kesamaan mendasar antara susunan dalaman jenis penipisan dan jenis peningkatan MOSFET, iaitu ketiadaan saluran yang semestinya merupakan bagian dari peranti ini.

Lapisan SiO2 dapat dilihat masih lazim, yang memastikan pengasingan antara pangkalan logam terminal gerbang dan wilayah antara saluran dan sumber. Namun, di sini dapat dilihat berdiri terpisah dari bahagian bahan jenis-p.

Dari perbincangan di atas kita dapat menyimpulkan bahawa susun atur dalaman MOSFET penipisan dan peningkatan mungkin mempunyai beberapa persamaan, kecuali saluran yang hilang antara saluran / sumber untuk jenis peningkatan MOSFET.

Operasi dan Karakteristik Asas

Untuk jenis peningkatan MOSFET apabila 0 V diperkenalkan pada VGSnya, kerana saluran n yang hilang (yang diketahui membawa banyak pembawa percuma) menyebabkan output semasa menjadi sifar, yang tidak seperti jenis penipisan MOSFET, mempunyai ID = IDSS.

Dalam situasi seperti ini kerana jalan yang hilang di terminal longkang / sumber, sejumlah besar pembawa dalam bentuk elektron tidak dapat terkumpul di longkang / sumber (kerana kawasan n-doped).

Menerapkan beberapa potensi positif pada VDS, dengan VGS ditetapkan pada voltan sifar dan terminal SS dipendekkan dengan terminal sumber, kita benar-benar menemui beberapa persimpangan pn bias terbalik antara kawasan n-doped dan substrat p untuk membolehkan sebarang konduksi yang ketara di seberang toskan ke sumber.

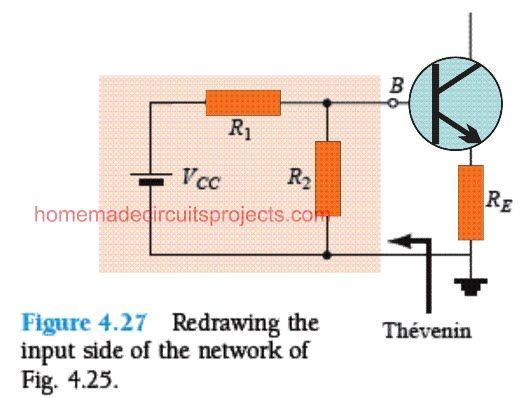

Dalam Rajah 5.32 menunjukkan keadaan di mana VDS dan VGS diterapkan dengan beberapa voltan positif lebih tinggi daripada 0 V, yang memungkinkan saluran dan pintu masuk berpotensi positif berkenaan dengan sumbernya.

Potensi positif di gerbang mendorong lubang di substrat p di sepanjang tepi lapisan SiO2 meninggalkan lokasi dan memasuki lebih dalam ke kawasan substrat p, seperti yang ditunjukkan pada gambar di atas. Ini berlaku kerana caj serupa yang saling menangkis.

Ini mengakibatkan kawasan penipisan diciptakan dekat dengan lapisan penebat SiO2 yang tidak mempunyai lubang.

Walaupun demikian, elektron p-substrat yang merupakan pembawa minoriti bahan ditarik ke arah gerbang positif dan mula berkumpul di kawasan yang dekat dengan permukaan lapisan SiO2.

Oleh kerana sifat penebat lapisan SiO2 pembawa negatif membolehkan pembawa negatif tidak diserap di terminal gerbang.

Ketika kita meningkatkan tahap VGS, ketumpatan elektron yang dekat dengan permukaan SiO2 juga meningkat, hingga akhirnya wilayah jenis-n yang diinduksi dapat memungkinkan pengaliran yang dapat diukur melintasi saluran / sumber.

Magnitudo VGS yang menyebabkan peningkatan optimum dalam arus pembuangan disebut sebagai voltan ambang, ditandakan dengan simbol VT . Dalam lembaran data anda akan dapat melihatnya sebagai VGS (Th).

Seperti yang dipelajari di atas, kerana tidak adanya saluran pada VGS = 0, dan 'ditingkatkan' dengan aplikasi voltan pintu-ke-sumber positif, MOSFET jenis ini dikenal sebagai MOSFET jenis peningkatan.

Anda akan mendapati bahawa kedua-dua MOSFET jenis penipisan dan peningkatan menunjukkan kawasan jenis peningkatan, tetapi istilahnya peningkatan digunakan untuk yang terakhir kerana secara khusus berfungsi menggunakan mod operasi peningkatan.

Sekarang, apabila VGS didorong melebihi nilai ambang, konsentrasi pembawa bebas akan meningkat di saluran di mana ia diinduksi. Ini menyebabkan arus pengaliran meningkat.

Sebaliknya, jika kita menjaga VGS tetap dan meningkatkan tahap VDS (voltan saliran ke sumber), ini akhirnya akan menyebabkan MOSFET mencapai titik tepu, seperti biasa juga terjadi pada JFET atau MOSFET yang berkurang.

Seperti yang ditunjukkan pada Gambar. 5.33 ID arus pembuangan akan diratakan dengan bantuan proses mencubit, ditunjukkan oleh saluran yang lebih sempit menuju hujung saluran saluran yang diinduksi.

Dengan menerapkan undang-undang voltan Kirchhoff pada voltan terminal MOSFET dalam Rajah 5.33, kami mendapat:

Sekiranya VGS tetap pada nilai tertentu, misalnya 8 V, dan VDS dinaikkan dari 2 hingga 5 V, voltan VDG oleh Persamaan. 5.11 dapat dilihat turun dari -6 hingga -3 V, dan potensi gerbang semakin kurang positif mengenai voltan saliran.

Tindak balas ini melarang pembawa atau elektron bebas menarik ke arah kawasan saluran yang diinduksi ini, yang seterusnya mengakibatkan penurunan lebar saluran yang efektif.

Pada akhirnya, lebar saluran menurun ke titik cubitan, mencapai keadaan tepu yang serupa dengan apa yang telah kita pelajari dalam artikel MOSFET penipisan sebelumnya.

Maknanya, meningkatkan VDS lebih jauh dengan VGS tetap tidak akan mempengaruhi tahap kepenuhan ID, hingga titik di mana keadaan kerosakan dicapai.

Melihat Gambar 5.34 kita dapat mengenal pasti bahawa untuk MOSFET seperti pada Gambar.5.33 yang mempunyai VGS = 8 V, saturasi berlaku pada tahap VDS 6 V. Untuk tepat tahap saturasi VDS dikaitkan dengan tahap VGS yang berlaku dengan:

Tidak diragukan lagi, ini menyiratkan bahawa apabila nilai VT tetap, peningkatan tahap VGS secara proporsional akan menyebabkan tahap tepu yang lebih tinggi untuk VDS melalui lokus tahap tepu.

Merujuk kepada ciri-ciri yang ditunjukkan dalam gambar di atas, tahap VT adalah 2 V, yang terbukti dengan fakta bahawa arus saliran telah jatuh ke 0 mA.

Oleh itu biasanya kita boleh mengatakan:

Apabila nilai VGS kurang dari tahap ambang untuk MOSFET jenis peningkatan, arus pengalirannya adalah 0 mA.

Kita juga dapat melihat dengan jelas dalam gambar di atas bahawa selagi VGS dinaikkan lebih tinggi dari VT hingga 8 V, tahap tepu yang sesuai untuk ID juga meningkat dari tahap 0 hingga 10 mA.

Lebih jauh lagi kita dapat memperhatikan bahawa jarak antara tahap VGS meningkat dengan peningkatan nilai VGS, menyebabkan kenaikan arus pengaliran yang semakin meningkat.

Kami dapati nilai arus keluar berkaitan dengan voltan pintu-ke-sumber untuk tahap VGS yang lebih besar daripada VT, melalui hubungan tidak linier berikut:

Istilah yang ditunjukkan sebagai tanda kurung kuadrat adalah istilah yang bertanggungjawab untuk hubungan tidak linear antara ID dan VGS.

Istilah k adalah pemalar dan merupakan fungsi susun atur MOSFET.

Kita dapat mengetahui nilai pemalar k ini melalui persamaan berikut:

di mana ID (hidup) dan VGD (aktif) masing-masing adalah nilai yang bergantung kepada ciri peranti.

Pada Rajah 5.35 berikutnya, kita dapati ciri-ciri pengaliran dan pemindahan disusun satu di sebelah yang lain untuk menjelaskan proses pemindahan antara satu sama lain.

Pada dasarnya, ia serupa dengan proses yang dijelaskan sebelumnya untuk JFET dan MOSFET jenis penipisan.

Walau bagaimanapun, untuk kes ini kita harus ingat bahawa arus pembuangan adalah 0 mA untuk VGS VT.

Di sini ID dapat melihat jumlah arus yang ketara, yang akan meningkat seperti yang ditentukan oleh Persamaan. 5.13.

Perhatikan, semasa menentukan titik-titik di atas ciri-ciri pemindahan dari ciri pembuangan, kami hanya mempertimbangkan tahap tepu. Ini mengehadkan kawasan operasi kepada nilai VDS yang lebih tinggi daripada tahap tepu seperti yang ditentukan oleh Persamaan. (5.12).

p-Saluran Peningkatan-Jenis MOSFET

Struktur MOSFET jenis peningkatan saluran-p seperti yang ditunjukkan pada Gambar 5.37a adalah kebalikan dari yang ditunjukkan pada Gambar 5.31.

Maksudnya, sekarang anda dapati bahawa substrat jenis-n dan kawasan-doped di bawah saliran dan sendi sumber.

Terminal tetap seperti yang ditetapkan, tetapi setiap arah semasa dan polariti voltan terbalik.

Ciri pembuangan dapat terlihat seperti yang ditunjukkan pada Gambar 5.37c, dengan peningkatan jumlah arus yang disebabkan oleh magnitud VGS yang semakin negatif.

Karakteristik pemindahan adalah kesan cermin (di sekitar sumbu ID) dari lengkung pemindahan Gambar 5.35, dengan peningkatan ID dengan semakin banyak nilai negatif VGS di atas VT, seperti yang ditunjukkan pada Gambar 5.37b. Persamaan (5.11) hingga (5.14) juga sesuai untuk peranti saluran-p.

Rujukan:

- https://en.wikipedia.org/wiki/MOSFET

- https://hi.wikipedia.org/wiki/%E0%A4%AE%E0%A5%89%E0%A4%B8%E0%A4%AB%E0%A5%87%E0%A4%9F

Sebelumnya: Litar Pengesan RF Anti Perisik - Pengesan Bug Tanpa Wayar Seterusnya: Memindahkan Karakteristik

![Diod Sentuhan Titik [Sejarah, Pembinaan, Litar Aplikasi]](https://electronics.jf-parede.pt/img/electronics-tutorial/38/point-contact-diodes-history-construction-application-circuit-1.jpg)