Catatan tersebut memperincikan kaedah yang berbeza untuk mengkonfigurasi rangkaian pembetulan faktor kuasa atau litar PFC dalam reka bentuk SMPS, dan menerangkan pilihan praktik terbaik untuk topologi ini sehingga mematuhi garis panduan sekatan PFC moden.

Merancang rangkaian bekalan kuasa yang cekap tidak pernah semudah itu, namun dalam jangka masa penyelidik dapat menyelesaikan sebahagian besar masalah yang berkaitan, dan dalam garis yang sama reka bentuk SMPS moden juga dioptimumkan dengan hasil yang terbaik, terima kasih kepada piawaian peraturan yang muncul yang memainkan peranan penting dalam menerapkan parameter kualiti yang lebih ketat untuk unit bekalan kuasa moden.

Garis Panduan PFC

Sekatan kualiti bekalan kuasa moden ditetapkan secara agresif, secara kolektif oleh usaha pengilang, pembekal dan badan pemerintah yang berkenaan.

Di antara banyak parameter kualiti yang ditetapkan untuk reka bentuk bekalan kuasa moden, pembetulan pembetulan faktor kuasa (PFC) yang sebenarnya dalam bentuk pembatalan harmonik telah dinyatakan sebagai syarat wajib oleh peraturan IEC 61000-3-2.

Oleh kerana pereka ini terpaksa menghadapi cabaran yang lebih sukar dalam merancang tahap pembetulan faktor kuasa dalam reka bentuk bekalan kuasa mereka untuk memenuhi undang-undang moden yang ketat ini, dan dengan bekalan kuasa semakin hebat dengan spesifikasi dan rangkaian aplikasinya, menyusun rangkaian PFC yang tepat tidak menjadi lebih mudah bagi banyak pengeluar di arena.

Tutorial yang disampaikan dikhaskan khas untuk semua persatuan dan profesional yang menceburkan diri dalam pembuatan atau merancang SMPS flyback kerana memudahkan mereka dengan reka bentuk dan pengiraan PFC yang paling sesuai mengikut keperluan masing-masing.

Perbincangan yang disertakan dalam tutorial ini akan membantu anda merancang litar PFC walaupun untuk unit yang besar dengan jarak sehingga 400 watt, 0,75 amp.

Pembaca juga akan mendapat peluang untuk belajar mengenai memilih penukar terpencil satu peringkat yang juga termasuk pemacu LED. Tutorial dan arahan reka bentuk langkah demi langkah bersama dengan perbandingan tahap sistem, banyak pereka yang terlibat secara aktif dalam bidang elektronik kuasa akan diberi pencerahan kepada lakukan dengan pendekatan yang paling optimum untuk keperluan aplikasi khusus mereka

Objektif Pembetulan Faktor Kuasa

Pengoptimuman litar pembetulan faktor kuasa dalam unit SMPS moden (mod suis bekalan kuasa) dapat berkembang sejak kebelakangan ini kerana munculnya sejumlah litar bersepadu terpadu (IC), yang memungkinkan untuk meletakkan reka bentuk PFC yang berbeza yang mempunyai spesifik mod operasi dan dengan keupayaan menangani cabaran individu.

Dengan peningkatan rangkaian topologi SMPS, kerumitan dalam perancangan dan pelaksanaan PFC juga bertambah buruk pada masa kini.

Dalam tutorial pertama, kita akan belajar mengenai perincian operasi reka bentuk yang paling disukai oleh para profesional.

Pada asasnya, pembetulan faktor kuasa membantu mengoptimumkan arus input dalam bekalan kuasa luar talian sehingga dapat meningkatkan daya sebenar dari input utama yang ada.

Sesuai dengan keperluan normal, alat elektrik tertentu harus meniru dirinya sebagai beban yang memiliki daya tahan murni, sehingga memungkinkan untuk memiliki daya reaktif sifar.

Keadaan ini mengakibatkan penghasilan arus harmonik input hampir sifar, dengan kata lain ia membenarkan arus yang digunakan sesuai dengan fasa voltan bekalan yang biasanya dalam bentuk gelombang sinus.

Pencapaian ini memudahkan alat untuk menggunakan 'kuasa sebenar' dari sumber listrik pada tahap yang paling optimum dan efisien, yang seterusnya akan meminimumkan pembaziran elektrik dan meningkatkan kecekapannya.

Penggunaan elektrik yang berkesan ini bukan sahaja membantu alat untuk tampil dengan cara yang paling cekap tetapi juga untuk syarikat utiliti dan peralatan modal yang terlibat untuk proses tersebut.

Ciri di atas juga membolehkan talian kuasa bebas dari harmonik dan gangguan yang dihasilkan dari semua peranti dalam rangkaian.

Selain daripada kelebihan yang disebutkan di atas, termasuk PFC dalam unit bekalan kuasa moden juga untuk memenuhi syarat peraturan seperti yang ditetapkan di Eropah dan Jepun dengan IEC61000-3-2 yang mana semua peralatan elektrik harus memenuhi syarat.

Keadaan yang disebutkan di atas telah diatur untuk sebagian besar peralatan elektronik yang mungkin dinilai di atas 75 watt di bawah piawaian peralatan Kelas D atau yang lebih tinggi lagi, yang menentukan amplitud tertinggi harmonik frekuensi garis antara harmonik ke-39.

Selain daripada piawaian ini, PFC juga digunakan untuk memastikan kecekapan lain seperti Energy Star 5.0 penting untuk komputer, dan Energy Star 2.0 untuk sistem Bekalan Kuasa dan set TV sejak tahun 2008.

Definisi Faktor Kuasa

Pembetulan faktor PFC atau Daya boleh didefinisikan sebagai nisbah daya nyata dengan daya nyata, dan dinyatakan sebagai:

PF = Kuasa Sebenar / Kuasa Rupa, di mana Kuasa Nyata dinyatakan dalam

Watt, sementara Power Apparent dinyatakan dalam VA.

Dalam ungkapan ini, daya sebenarnya ditentukan sebagai purata produk arus dan voltan seketika dalam satu fasa atau kitaran, sementara daya yang nyata dianggap sebagai nilai RMS semasa voltan.

Ini menunjukkan bahawa apabila pasangan arus dan voltan sinusoidal dan berada dalam fasa satu sama lain, faktor daya yang dihasilkan adalah 1.0.

Namun, dalam keadaan ketika arus, parameter voltan sinusoidal tetapi tidak dalam fasa, menimbulkan faktor daya yang merupakan kosinus dari sudut fasa.

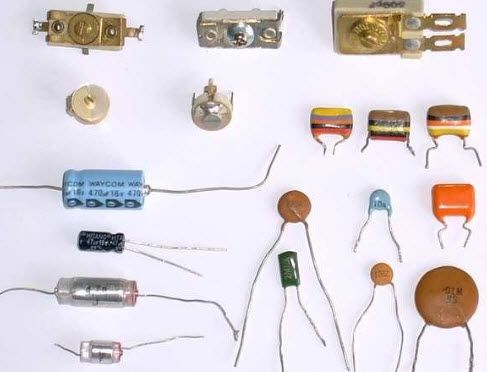

Keadaan faktor daya yang dijelaskan di atas berlaku dalam keadaan di mana voltan dan arus keduanya adalah gelombang sinus tulen, bersamaan dengan keadaan di mana beban yang menyertainya terdiri dari komponen resistif, induktif dan kapasitif yang mungkin semuanya tidak linear, tidak menyesuaikan diri dengan parameter arus dan voltan masukan.

Topologi SMPS biasanya memperkenalkan impedans tak linier ke dalam talian utama kerana rangkaian litarnya yang dijelaskan di atas.

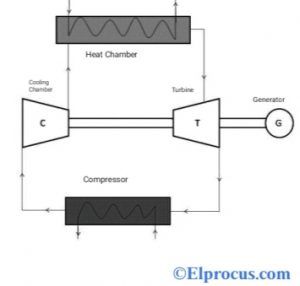

Bagaimana SMPS Berfungsi

Litar SMPS pada dasarnya merangkumi tahap penyearah pada input yang boleh berupa gelombang separuh atau penyearah gelombang penuh dan kapasitor penapis pelengkap untuk menahan voltan yang dibetulkan melintasi hingga tahap puncak gelombang sinus bekalan sehingga masa puncak berikutnya gelombang sinus muncul dan mengulangi kitaran pengisian kapasitor ini, menghasilkan voltan pemalar puncak yang diperlukan di atasnya.

Proses pengisian kapasitor ini pada setiap putaran puncak AC menuntut agar input mesti dilengkapi dengan arus yang cukup untuk memenuhi penggunaan beban SMPS, di antara selang puncak ini.

Kitaran ini dilaksanakan dengan membuang arus besar ke kapasitor dengan cepat, yang diterapkan pada beban dengan melakukan pembuangan hingga siklus puncak berikutnya tiba.

Untuk corak pengecasan dan pengosongan yang tidak sekata ini, disarankan agar arus nadi dari kapasitor dinilai 15% lebih tinggi daripada keperluan purata beban.

Kita dapat melihat pada rajah di atas bahawa walaupun terdapat banyak penyelewengan, voltan dan parameter semasa nampaknya saling fasa.

Namun jika kita menerapkan istilah 'fasa sudut kosinus' untuk hal di atas akan menimbulkan kesimpulan yang salah mengenai bekalan kuasa yang mempunyai faktor daya 1.0

Bentuk gelombang atas dan bawah menunjukkan jumlah kandungan harmonik arus.

Di sini 'kandungan harmonik asas' ditunjukkan dibandingkan dengan amplitudo 100%, sementara harmonik yang lebih tinggi disajikan sebagai peratusan tambahan dari amplitud asas.

Walau bagaimanapun, kerana kuasa sebenarnya hanya ditentukan oleh komponen asas, sedangkan harmonik tambahan hanya mewakili kekuatan yang nyata, faktor kuasa sebenarnya mungkin di bawah 1.0.

Kami menyebut penyimpangan ini dengan istilah faktor distorsi yang secara asasnya bertanggungjawab untuk menimbulkan faktor kuasa tidak kesatuan dalam unit SMPS.

Ungkapan untuk Kekuatan Sebenar dan Nyata

Ungkapan umum yang membahas hubungan antara kekuatan nyata dan kekuatan nyata dapat diberikan seperti berikut:

Di mana cosΦ membentuk faktor anjakan yang muncul dari sudut fasa Φ antara bentuk gelombang arus / voltan dan cosΦ menandakan faktor distorsi.

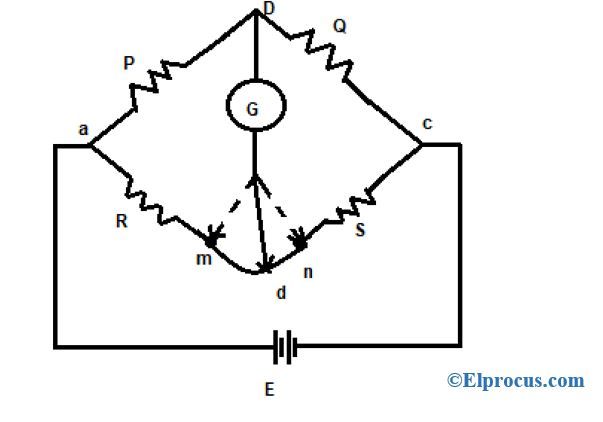

Dengan merujuk kepada rajah di bawah, kita dapat menyaksikan situasi yang menunjukkan pembetulan faktor kuasa yang sempurna.

Kita dapat melihat bahawa di sini bentuk gelombang semasa dengan idealnya meniru bentuk gelombang voltan kerana kedua-duanya nampaknya berjalan dalam fasa dan selaras antara satu sama lain.

Oleh itu di sini harmonik arus input boleh dianggap hampir sifar.

Pembetulan Faktor Kuasa V Pengurangan Harmonik

Melihat ilustrasi terdahulu, jelas bahawa faktor kuasa dan harmonik rendah berfungsi selaras antara satu sama lain.

Umumnya dirasakan bahawa jika had untuk harmonik masing-masing digariskan dapat membantu menyekat pencemaran arus masukan pada saluran kuasa dengan cara menghilangkan gangguan arus gangguan dengan peralatan lain di sekitarnya.

Oleh itu, sementara pemprosesan arus input dapat disebut sebagai 'pembetulan faktor kuasa', keluaran penyempurnaan berpendapat bahawa pemprosesan ini difahami sebagai kandungan harmonik mengikut garis panduan antarabangsa.

Untuk topologi SMPS, biasanya elemen perpindahan kira-kira pada kesatuan, menimbulkan hubungan berikut antara faktor kuasa dan penyelewengan harmonik.

Dalam ungkapan THD mewakili Total Harmonic Distortion sebagai jumlah kuadrat harmonik berbahaya berbanding kandungan asas, menyatakan berat relatif kandungan harmonik yang berkaitan dengan merujuk kepada rakan asas. Persamaan lain mengaitkan angka mutlak THD dan bukan dalam perkadaran%, menyatakan bahawa THD pada dasarnya harus sifar untuk mewujudkan PF kesatuan.

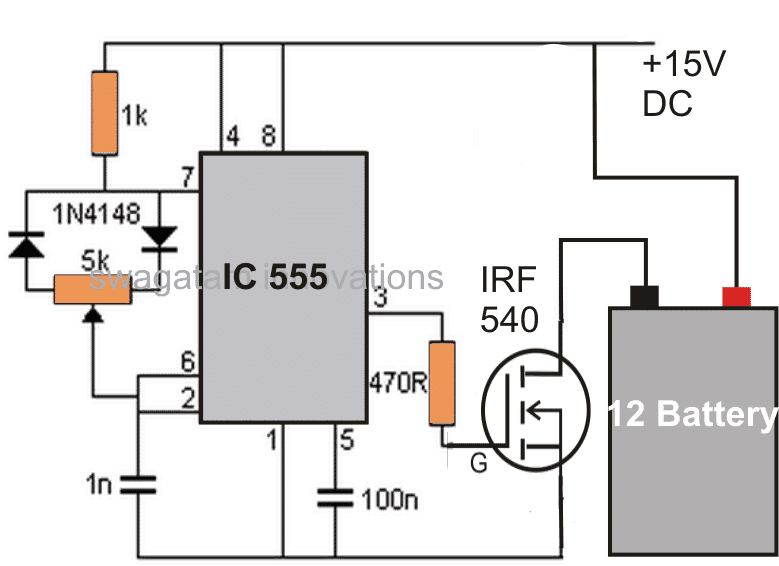

Jenis Pembetulan Faktor Kuasa

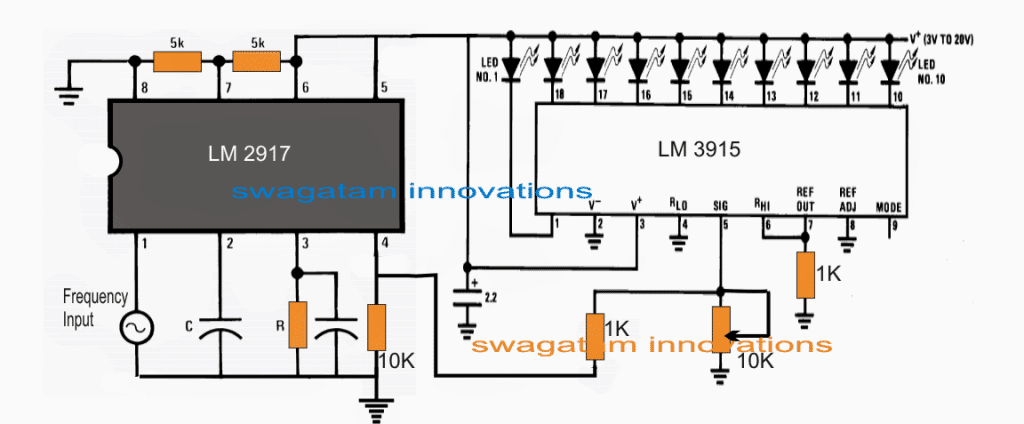

Karakteristik bentuk gelombang input pada gambar di atas menunjukkan jenis pembetulan faktor daya khas 'aktif' untuk peranti SMPS yang diperkenalkan di antara konfigurasi penerus input dan kapasitor penapis, dan melalui litar bersepadu PFC yang mengawal proses bersama dengan litar yang terkait untuk memastikan bahawa arus input secara kohesif mengikuti bentuk gelombang voltan input.

Jenis pemprosesan ini dapat dianggap sebagai jenis PFC yang paling lazim digunakan dalam litar SMPS moden, seperti yang dapat disaksikan pada gambar di bawah.

Setelah itu, tidak wajib hanya versi 'aktif' yang menggunakan IC, dan semikonduktor untuk PFC yang dicadangkan, bentuk reka bentuk lain yang dapat menjamin jumlah PFC yang wajar di bawah peraturan yang ditetapkan biasanya disambut baik.

Telah diperhatikan bahawa sebenarnya satu induktor yang menggantikan kedudukan rakan yang 'aktif' mampu menolak harmonik dengan memuaskan dengan mengawal puncak dan dengan menyalurkan arus secara seragam selaras dengan voltan masukan dengan cukup cekap.

Reka Bentuk PFC Pasif

Walau bagaimanapun, bentuk kawalan PFC pasif ini dapat menuntut induktor berpori besi yang sangat besar dan oleh itu dapat digunakan untuk aplikasi di mana kekompakan bukanlah syarat penting. (halaman 12)

Induktor tunggal pasif sepertinya merupakan penyelesaian cepat untuk PFC tetapi untuk aplikasi watt tinggi ukurannya mulai tidak menarik kerana dimensi yang sangat besar.

Dalam grafik di bawah ini kita dapat menyaksikan ciri input tiga nombor varian SMPS PC 250 watt, masing-masing mewakili bentuk gelombang semasa pada faktor skala yang setara.

Kita dapat dengan mudah melihat bahawa hasil yang diperoleh dari PFC berdasarkan induktor pasif adalah puncak arus 33% lebih tinggi, berbanding dengan rakan penapis PFC aktif.

Walaupun ini mungkin dapat melepasi piawaian IEC61000-3-2, ia pasti tidak setara dengan peraturan syarat 0.9PF yang lebih ketat baru-baru ini, dan akan gagal tahap penerimaan QC, yang ditetapkan sesuai dengan standard baru ini.

Rajah Blok Asas

Oleh kerana trend pasaran elektronik yang berterusan di mana kita dapat melihat kenaikan kos tembaga bersama dengan kenaikan proses teras magnetik dan pengenalan bahan semikonduktor moden yang jauh lebih murah, tidak akan mengejutkan jika kita melihat pendekatan PFC aktif menjadi sangat popular daripada rakan pasif.

Dan trend ini dapat dilihat berkembang lebih kuat di masa depan, menghadirkan penyelesaian PFC yang lebih maju dan lebih baik untuk banyak pereka dan pengeluar SMPS.

Membandingkan Harmonik Garis Input dengan Piawaian IEC610003-2

Dalam Rajah di bawah ini kita dapat melihat jejak tiga hasil SMPS PC 250 watt yang berasingan dengan merujuk kepada sekatan IEC6000-3-2. Sekatan yang ditunjukkan berlaku untuk semua alat kelas D seperti PC, TV, dan monitornya.

Had kandungan harmonik yang ditunjukkan ditetapkan sesuai dengan daya input peranti. Untuk produk yang berkaitan dengan lampu seperti lampu LED, lampu CFL, sekatan kelas C biasanya diikuti, yang sama dengan had watt input mereka.

Produk elektronik bukan konvensional lain mendapati had PFC mereka ditetapkan berkadar dengan daya input minimum 600 watt.

Sekiranya kita melihat jejak PFC pasif, kita merasa hampir tidak sesuai dengan had sekatan yang ditetapkan, hanya situasi sentuhan dan sentuhan (di harmonik no3)

Menganalisis Ciri-ciri PFC Pasif

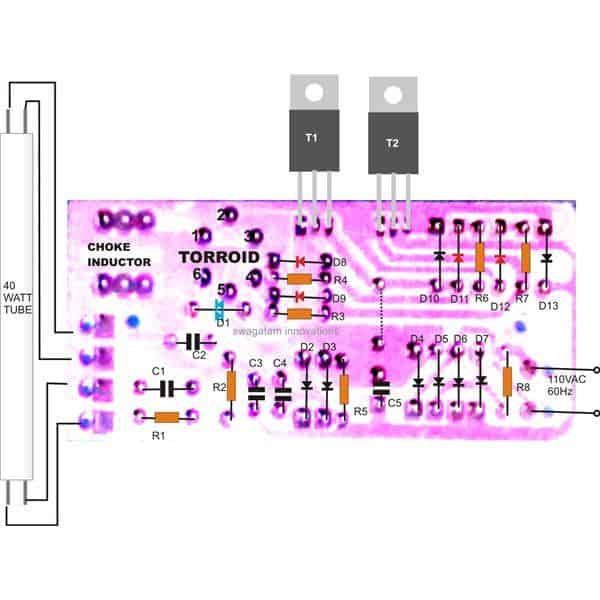

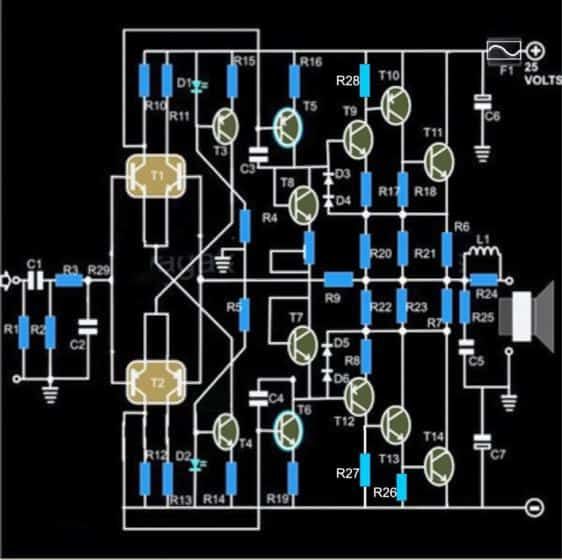

Dalam gambar berikut kita dapat melihat contoh klasik litar PFC pasif yang direka untuk bekalan kuasa PC tradisional. Perkara yang dapat diperhatikan di sini ialah penyambungan paip pusat induktor PFC dengan voltan masukan saluran input.

Semasa dalam mod pilihan 220V (buka terbuka), keseluruhan dua bahagian induktor diterapkan dengan rangkaian penerus berfungsi seperti litar penerus jambatan penuh.

Namun dalam mod 110V (tutup dekat), hanya 50% atau satu setengah gegelung digunakan melalui bahagian kiri gegelung yang sedang dilaksanakan sedangkan bahagian penerus sekarang diubah menjadi rangkaian pengganda penyearah gelombang separuh.

Oleh kerana pemilihan 220V pasti menghasilkan sekitar 330V setelah pembetulan gelombang penuh, ini membentuk input bus untuk SMPS dan memiliki kemungkinan turun naik secara signifikan sesuai dengan voltan saluran input.

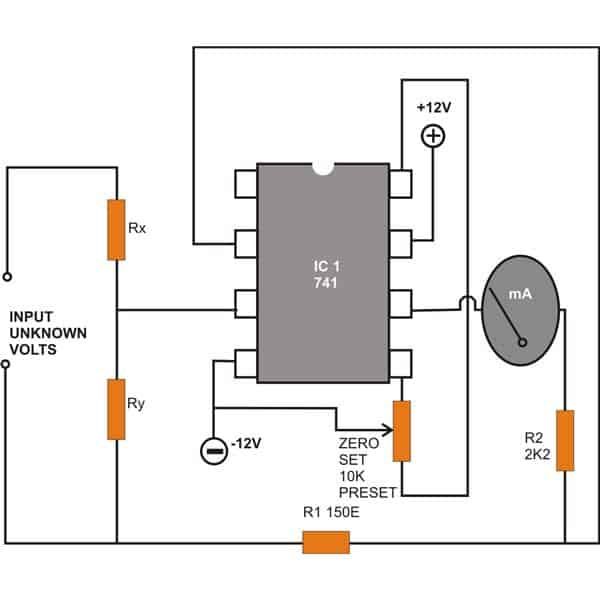

Rajah Litar Contoh

Walaupun reka bentuk PFC pasif ini mungkin kelihatan cukup sederhana dan mengagumkan dengan prestasinya, ia mungkin menunjukkan beberapa kekurangan yang ketara.

Seiring dengan sifat PFC yang besar, dua perkara lain yang mempengaruhi kinerjanya adalah yang pertama, penyertaan suis mekanikal yang menjadikan sistem terdedah kepada kemungkinan kesalahan manusia semasa mengendalikan unit, dan juga masalah haus dan kerosakan yang berkaitan.

Kedua, voltan saluran yang tidak stabil menghasilkan ketidakcekapan relatif di bahagian depan keberkesanan kos dan ketepatan penukaran kuasa DC ke DC yang dihubungkan dengan output PFC.

Pengawal Mod Pengaliran Kritikal (CrM)

Tahap pengawal yang disebut mod konduksi kritikal yang juga disebut sebagai mod peralihan atau mod konduksi garis batas (BCM) adalah konfigurasi litar yang dapat didapati digunakan secara efektif dalam aplikasi elektronik pencahayaan. Walaupun bebas dari kegunaannya, alat kawalan ini agak mahal.

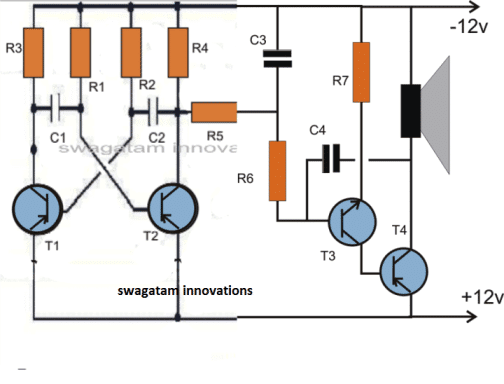

Gambar rajah 1-8 berikut menunjukkan reka bentuk litar pengawal CrM biasa.

Biasanya pengawal CrM PFC akan mempunyai jenis litar yang ditunjukkan di atas, yang dapat difahami dengan bantuan perkara berikut:

Input tahap pengganda rujukan menerima isyarat dimensi yang tepat dari output penguat ralat yang berkaitan yang mempunyai kutub frekuensi rendah.

Input pengganda yang lain dapat dilihat dirujuk dengan tegangan terpendam DC yang stabil yang diekstrak dari input saluran AC yang diperbaiki.

Oleh itu, output yang dihasilkan dari pengganda adalah produk DC relatif dari output amp kesalahan dan isyarat yang dirujuk dalam bentuk gelombang sinus AC gelombang penuh dari input AC.

Keluaran ini dari tahap pengganda dapat dilihat juga dalam bentuk gelombang gelombang sinus gelombang penuh tetapi dikurangkan dengan tepat sesuai dengan penggunaan isyarat kesalahan (faktor keuntungan) yang digunakan sebagai rujukan untuk voltan masukan.

Amplitud isyarat sumber ini diubah dengan tepat untuk menerapkan daya rata-rata yang ditentukan dan memastikan voltan keluaran yang diatur dengan betul.

Tahap yang bertanggung jawab untuk memproses amplitud arus menyebabkan arus mengalir sesuai dengan bentuk gelombang keluaran dari pengganda, namun amplitud sinyal arus frekuensi garis (setelah melicinkan) diharapkan dapat setengah dari rujukan ini dari tahap pengganda .

Di sini, operasi dengan membentuk arus litar dapat difahami seperti berikut:

Merujuk pada rajah di atas, Vref bermaksud isyarat keluar dari tahap pengganda, yang selanjutnya disalurkan ke salah satu opamp pembanding yang input kedua dirujuk dengan isyarat bentuk gelombang semasa.

Pada suis kuasa, arus melintasi induktor perlahan-lahan meningkat sehingga isyarat merentasi shunt telah mencapai tahap Vref.

Ini memaksa pembanding untuk menukar outputnya dari On ke OFF mematikan kuasa ke litar.

Sebaik sahaja ini berlaku, voltan yang secara beransur-ansur melintasi induktor mula turun perlahan ke arah sifar dan setelah menyentuh sifar, output opamp kembali dan dihidupkan kembali, dan kitaran terus berulang.

Seperti namanya ciri khas di atas, corak kawalan sistem tidak pernah membenarkan arus induktor untuk menembak melebihi had yang telah ditentukan melintasi mod pensuisan berterusan dan tidak berterusan.

Susunan ini membantu untuk meramalkan dan mengira hubungan antara tahap arus puncak rata-rata output yang dihasilkan dari opamp. Oleh kerana tindak balas adalah dalam bentuk gelombang segitiga, rata-rata bentuk gelombang menunjukkan tepat 50% puncak sebenar bentuk gelombang segitiga.

Ini menunjukkan bahawa nilai purata yang dihasilkan dari isyarat arus gelombang segitiga ialah = Arus induktor x R atau hanya meletakkan separuh daripada tahap rujukan yang telah ditetapkan (Vref) opamp.

Kekerapan pengawal selia menggunakan prinsip di atas akan bergantung pada voltan saluran dan arus beban. Kekerapannya mungkin jauh lebih tinggi pada voltan saluran yang lebih tinggi dan boleh berbeza-beza apabila input garis berbeza.

Mod Pengaliran Kritikal Frekuensi Dikepit (FCCrM)

Walaupun popularitinya dalam pelbagai aplikasi kawalan PFC bekalan kuasa industri, pengawal CrM yang dijelaskan di atas melibatkan beberapa kekurangan yang wujud.

Kelemahan utama jenis kawalan PFC aktif ini adalah ketidakstabilan frekuensinya sehubungan dengan keadaan garis dan beban, yang menunjukkan peningkatan frekuensi dengan beban yang lebih ringan dan voltan saluran yang lebih tinggi, dan juga pada setiap kali gelombang sinus input mendekati persilangan sifar.

Sekiranya usaha dilakukan untuk memperbaiki masalah ini dengan menambahkan penjepit frekuensi, menghasilkan output dengan bentuk gelombang arus yang terdistorsi, yang sepertinya tidak dapat dihindari kerana fakta bahawa 'Ton' tetap tidak disesuaikan untuk prosedur ini.

Walau bagaimanapun, pengembangan teknik alternatif membantu mencapai pembetulan faktor kuasa yang sebenarnya walaupun dalam mod tidak bersambung (DCM). Prinsip operasi boleh dikaji dalam Rajah di bawah dan dengan persamaan yang dilampirkan.

Merujuk pada rajah di atas, arus puncak gegelung dapat dinilai dengan menyelesaikan:

Arus gegelung rata-rata dengan merujuk kepada kitaran pensuisan (yang juga dianggap sebagai arus talian sesaat untuk kitaran pensuisan yang diberikan, disebabkan oleh fakta bahawa frekuensi pensuisan biasanya lebih tinggi daripada frekuensi garis di mana variasi voltan saluran berlaku , dinyatakan dengan formula:

Menggabungkan hubungan di atas dan penyederhanaan syarat memberikan yang berikut:

Ungkapan di atas dengan jelas menunjukkan dan menyiratkan bahawa sekiranya kaedah dilaksanakan di mana algoritma menjaga ton.tcycle / Tsw pada tahap yang tetap, ia akan membolehkan kita mencapai arus garis gelombang sinus yang mempunyai faktor daya kesatuan walaupun dalam keadaan tidak berterusan mod operasi.

Walaupun pertimbangan di atas menunjukkan beberapa faedah yang berbeza untuk teknik pengawal DCM yang dicadangkan, sepertinya bukan pilihan yang tepat kerana tahap arus puncak tinggi yang berkaitan, seperti yang ditunjukkan dalam jadual berikut:

Untuk mencapai keadaan PFC yang ideal, pendekatan yang masuk akal adalah untuk menerapkan keadaan di mana modus operasi DCM dan Crm digabungkan untuk memerah hasil terbaik dari dua rakan sejawat ini.

Oleh itu apabila keadaan beban tidak berat dan CrM berjalan pada frekuensi tinggi, litar berjalan untuk mod operasi DCM, dan sekiranya arus beban tinggi, keadaan Crm dibiarkan berterusan sehingga puncak arus tidak cenderung melepasi had tinggi yang tidak diingini.

Pengoptimuman jenis ini di antara dua mod kawalan yang dicadangkan dapat dilihat dengan baik dalam gambar berikut di mana faedah dari dua mod kawalan digabungkan untuk mencapai penyelesaian yang paling diingini.

Terus Mod Pengaliran

Mod konduksi berterusan PFC boleh menjadi sangat popular dalam reka bentuk SMPS kerana ciri dan rangkaian aplikasi mereka yang fleksibel dan beberapa kelebihan yang berkaitan.

Dalam mod ini tegangan puncak semasa dikekalkan pada tahap yang lebih rendah sehingga menyebabkan kerugian pengalihan yang minimum dalam komponen yang berkaitan, dan selanjutnya riak input diberikan pada tahap minimum dengan frekuensi yang relatif tetap, yang seterusnya memungkinkan proses melicinkan jauh lebih sederhana untuk sama.

Atribut berikut yang berkaitan dengan CCM jenis CCM perlu dibincangkan dengan lebih terperinci.

Kawalan Vrms2

Salah satu sifat penting dengan kebanyakan reka bentuk PFC yang diterapkan secara universal adalah isyarat rujukan yang perlu menjadi tiruan turun naik dari voltan input yang diperbaiki.

Minimum yang diperbaiki setara voltan masukan ini akhirnya digunakan dalam litar untuk membentuk bentuk gelombang yang betul untuk arus keluaran.

Seperti yang telah dibahas di atas, tahap litar pengganda biasanya digunakan untuk operasi ini, tetapi seperti yang kita ketahui bahawa tahap litar pengganda mungkin lebih efektif dari segi kos daripada sistem pengganda input twn tradisional.

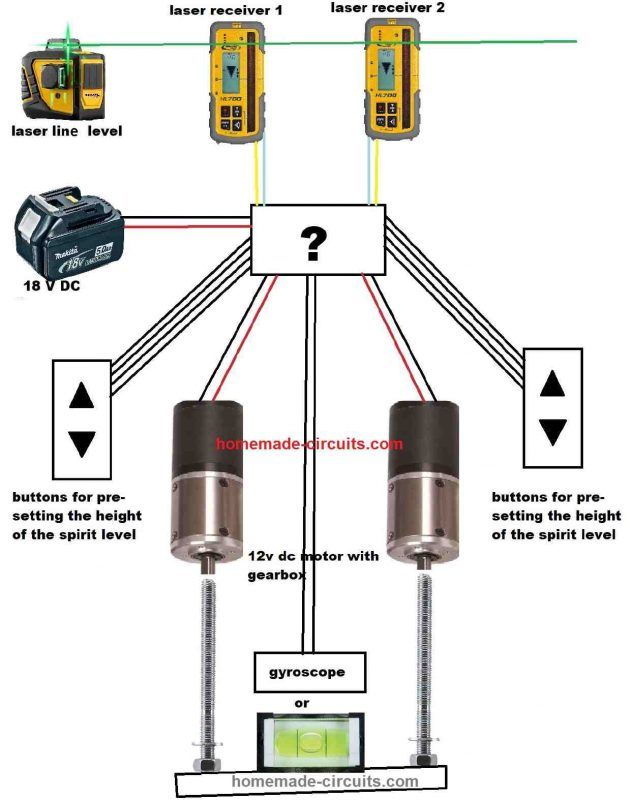

Susun atur contoh klasik dapat dilihat dalam Rajah di bawah yang menunjukkan pendekatan PFC mod berterusan.

Seperti yang dapat dilihat, di sini penukar dorongan dipicu dengan bantuan mod arus PWM rata-rata, yang menjadi bertanggungjawab untuk dimensi arus induktor (arus masukan untuk penukar), dengan merujuk kepada isyarat arus perintah, V (i) , yang dapat dilihat sebagai setara pengurangan voltan masukan V (dalam) dengan bahagian VDIV.

Ini dilaksanakan dengan membagi isyarat voltan ralat dengan kuadrat isyarat voltan input (dilicinkan oleh kapasitor Cf, untuk membuat faktor penskalaan yang dipermudah dengan merujuk pada tahap voltan input).

Walaupun anda merasa agak canggung untuk melihat isyarat ralat dibahagi dengan kuadrat voltan masukan, alasan di sebalik ukuran ini adalah untuk membuat gelung (atau tindak balas bergantung sementara) yang mungkin tidak berdasarkan voltan masukan mencetuskan.

Kuadrat voltan pada penyebut meneutralkan dengan nilai Vsin bersamaan dengan fungsi pemindahan kawalan PWM (proporsionaliti arus lereng graf perangsang dengan voltan masukan).

Namun salah satu kelemahan bentuk PFC ini adalah fleksibiliti pengganda, yang memaksa tahap ini sedikit berlebihan terutama bahagian pengendalian kuasa litar, sehingga dapat mengekalkan senario pelesapan kuasa terburuk.

Kawalan Mod Semasa Purata

Pada gambar di atas kita dapat melihat bagaimana isyarat rujukan yang dihasilkan dari pengganda V (i) menandakan bentuk bentuk gelombang, dan julat penskalaan arus input PFC.

Tahap PWM yang ditunjukkan menjadi bertanggungjawab untuk memastikan arus input rata-rata setara dengan nilai rujukan. Prosedur ini dilaksanakan melalui tahap pengawal mod arus rata-rata, seperti yang dapat dilihat pada gambar yang diberikan di bawah.

Pengendalian mod arus rata-rata pada dasarnya dikonfigurasi untuk mengatur arus rata-rata (input / output) dengan merujuk kepada isyarat kawalan Icp, yang seterusnya dibuat dengan menggunakan gelung DC frekuensi rendah melalui tahap litar penguat ralat, dan ini hanyalah arus setara yang sepadan dengan isyarat Vi yang ditunjukkan pada rajah sebelumnya hingga ini.

Penguat arus tahap berfungsi sebagai pengintegrasi arus dan juga penguat kesalahan, untuk mengatur bentuk bentuk gelombang, sedangkan sinyal Icp yang dihasilkan melintasi Rcp menjadi bertanggung jawab untuk melaksanakan kontrol voltan input DC.

Untuk memastikan tindak balas linier dari penguat semasa, inputnya harus serupa, yang bermaksud perbezaan potensi yang dihasilkan di R (shunt) harus serupa dengan voltan yang dihasilkan di sekitar Rcp, kerana kita tidak dapat memiliki DC melalui input perintang bukan pembalik penguat semasa.

Output yang dihasilkan oleh penguat semasa seharusnya merupakan isyarat ralat 'frekuensi rendah' bergantung pada arus rata shunt, serta isyarat dari Isp.

Kini pengayun menghasilkan isyarat gigi gergaji yang digunakan untuk membandingkan isyarat di atas dengannya, seperti yang dilakukan dengan reka bentuk kawalan mod voltan.

Ini menghasilkan penciptaan PWM yang ditentukan dengan membandingkan dua isyarat yang disebutkan di atas.

Penyelesaian PFC Lanjutan

Pelbagai kaedah kawalan PFC seperti yang dibahas di atas (CrM, CCM, DCM) dan variannya memberikan para perancang dengan pelbagai pilihan untuk mengkonfigurasi rangkaian PFC.

Namun di sebalik pilihan ini, pencarian yang konsisten untuk mencapai modul yang lebih baik dan lebih maju dari segi kecekapan telah memungkinkan reka bentuk yang lebih canggih didiagnosis untuk aplikasi ini.

Kami akan membincangkan lebih lanjut mengenai perkara ini kerana artikel ini dikemas kini dengan yang terkini mengenai perkara ini.

Sebelumnya: Cara Memilih Pengecas yang Tepat untuk Bateri Li-Ion Seterusnya: Litar Rickshaw Solar E