Mengasingkan terminal transistor bipolar menggunakan rangkaian pembahagi resistif yang dikira untuk memastikan prestasi optimum dan tindak balas pensuisan disebut biasing pembahagi voltan.

Di dalam reka bentuk berat sebelah sebelumnya bahawa kita belajar arus berat sebelah saya CQ dan voltan V CEQ adalah fungsi keuntungan semasa (β) BJT.

Tetapi, seperti yang kita ketahui bahawa β dapat rentan terhadap perubahan suhu, terutama untuk transistor silikon, dan juga nilai sebenarnya beta sering tidak dikenal pasti dengan tepat, disarankan untuk mengembangkan bias voltan-Pembahagi dalam rangkaian BJT yang mungkin kurang terdedah kepada suhu, atau, bebas daripada beta BJT itu sendiri.

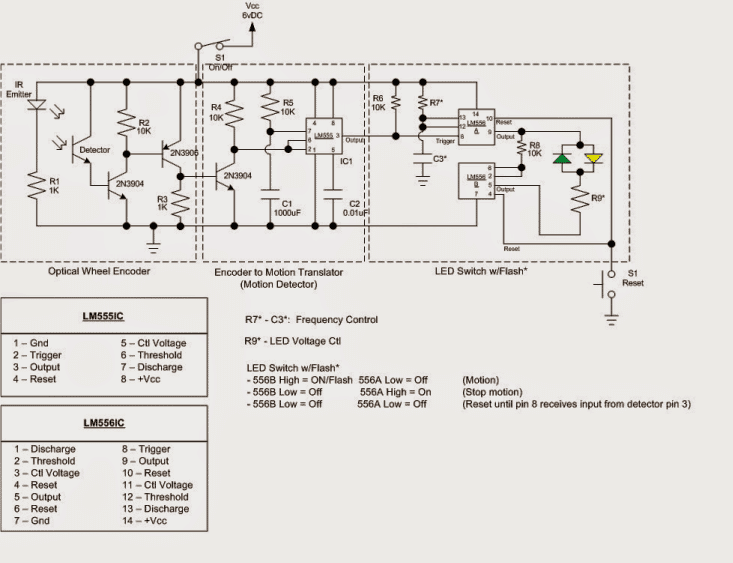

Susunan bias pembahagi voltan pada Rajah 4.25 boleh dianggap sebagai salah satu reka bentuk ini.

Apabila diperiksa dengan asas tepat kerentanan terhadap variasi beta kelihatan sangat sederhana. Sekiranya pemboleh ubah litar dikendalikan dengan tepat, tahap I CQ dan V CEQ boleh sepenuhnya bebas daripada beta.

Ingatlah dari penjelasan sebelumnya bahawa titik-Q ditandai dengan tahap tetap ICQ dan VCEQ seperti yang ditunjukkan dalam Rajah 4.26.

Tahap I BQ boleh berubah bergantung pada variasi dalam beta, tetapi titik operasi di sekitar ciri-ciri yang dikenal pasti oleh I CQ dan V CEQ boleh berubah dengan mudah sekiranya garis panduan litar yang sesuai digunakan.

Seperti yang telah disebutkan di atas, anda akan menemui beberapa pendekatan yang boleh digunakan untuk menyelidiki penyediaan pembahagi voltan.

Sebab di sebalik pemilihan nama khusus untuk litar ini akan menjadi jelas semasa analisis kami, dan akan dibincangkan dalam catatan akan datang.

Yang pertama adalah teknik tepat yang boleh dilakukan pada sebarang penyediaan pembahagi voltan.

Yang kedua dipanggil kaedah anggaran, dan pelaksanaannya dapat dilaksanakan apabila faktor-faktor tertentu dipenuhi. The pendekatan anggaran membolehkan analisis yang lebih langsung dengan usaha dan masa minimum.

Selain itu, ini sangat berguna untuk 'mod reka bentuk' yang akan kita bincangkan di bahagian kemudian.

Secara keseluruhan, sejak 'pendekatan anggaran' dapat diusahakan dengan sebilangan besar syarat dan oleh itu mesti dinilai dengan tahap perhatian yang sama dengan 'kaedah tepat'.

Analisis Tepat

Mari belajar bagaimana kaedah analisis tepat dapat dilaksanakan dengan penjelasan berikut

Mengacu pada gambar berikut, sisi input jaringan dapat dibuat ulang seperti yang digambarkan pada Gambar 4.27 untuk analisis dc.

The Setaraf Thévenin rangkaian untuk reka bentuk di sebelah kiri pangkalan BJT B kemudian dapat ditentukan dengan cara seperti yang digambarkan di bawah:

RTh : Titik bekalan input digantikan oleh litar pintas yang setara seperti yang ditunjukkan dalam Rajah 4.28 di bawah.

ETH: Sumber voltan bekalan V DC digunakan kembali ke litar, dan voltan Thévenin litar terbuka seperti yang ditunjukkan dalam Rajah 4.29 di bawah dinilai seperti yang diberikan di bawah:

Melaksanakan peraturan pembahagi voltan, kita sampai pada persamaan berikut:

Seterusnya, dengan membuat reka bentuk Thévenin seperti yang digambarkan dalam Rajah 4.30, kami menilai I BQ dengan menggunakan undang-undang voltan Kirchhoff terlebih dahulu mengikut arah jam untuk gelung:

ETh - IBRTh - VBE - IERE = 0

Seperti yang kita tahu IE = (β + 1) B Menggantikannya di gelung di atas dan menyelesaikan untuk I B memberi:

Persamaan. 4.30

Pada pandangan pertama anda mungkin merasakan Persamaan. (4.30) kelihatan sangat berbeza dari persamaan lain yang dikembangkan sejauh ini, namun tampilan yang lebih dekat akan menunjukkan bahawa pengangka hanya perbezaan dua tahap volt, sedangkan penyebutnya adalah hasil dari rintangan dasar + perintang pemancar, yang dipantulkan oleh (β + 1) dan tidak diragukan lagi sangat serupa dengan Persamaan. (4.17) ( Gelung Pemancar Asas )

Setelah IB dikira melalui persamaan di atas, selebihnya magnitud dalam reka bentuk dapat dikenal pasti melalui kaedah yang sama seperti yang kita lakukan untuk rangkaian bias pemancar, seperti yang ditunjukkan di bawah:

Persamaan (4.31)

Menyelesaikan Contoh Praktikal (4.7)

Hitung voltan bias DC V INI dan I semasa C dalam rangkaian pembahagi voltan yang ditunjukkan di bawah Rajah 4.31

Rajah 4.31 Litar distabilkan beta untuk Contoh 4.7.

Analisis anggaran

Di bahagian di atas, kami mempelajari 'kaedah tepat', di sini kami akan membincangkan 'kaedah anggaran' untuk menganalisis pembahagi voltan litar BJT.

Kita dapat melukis tahap input rangkaian pembahagi voltan berdasarkan BJT seperti yang ditunjukkan pada gambar 4.32 di bawah.

Rintangan Ri boleh dianggap sebagai rintangan yang setara antara garis dasar dan landasan litar, dan RE sebagai perintang antara pemancar dan tanah.

Dari perbincangan kami sebelumnya [Pers. (4.18)] kita tahu bahawa rintangan yang dihasilkan atau dipantulkan antara asas / pemancar BJT dijelaskan oleh persamaan Ri = (β + 1) RE.

Sekiranya kita mempertimbangkan situasi di mana Ri jauh lebih besar daripada rintangan R2, akan mengakibatkan IB relatif lebih kecil daripada I2 (ingat arus selalu berusaha mencari dan bergerak ke arah rintangan minimum), dan dengan itu I2 akan berubah kira-kira sama dengan I1.

Memandangkan nilai anggaran IB pada dasarnya adalah sifar sehubungan dengan I1 atau I2, maka I1 = I2, dan R1, dan R2 dapat dianggap sebagai elemen siri.

Rajah 4.32 Litar separa-bias untuk mengira voltan asas perkiraan V B .

Voltan merentasi R2, yang pada asalnya voltan asas dapat dinilai seperti yang ditunjukkan di bawah, dengan menerapkan rangkaian peraturan pembahagi voltan:

Sekarang sejak Ri = (β + 1) RE ≅ b RE, keadaan yang mengesahkan sama ada pelaksanaan kaedah anggaran boleh dilaksanakan atau tidak ditentukan oleh persamaan:

Ringkasnya, jika nilai RE kali ganda dari nilai β, tidak kurang dari 10 kali nilai R2, maka boleh diizinkan untuk melaksanakan analisis perkiraan dengan ketepatan optimum

Setelah VB dinilai, magnitud VE dapat ditentukan oleh persamaan:

sementara arus pemancar dapat dikira dengan menggunakan formula:

Voltan dari pemungut ke pemancar dapat dikenal pasti dengan menggunakan formula berikut:

VCE = VCC - ICRC - IERE

Walau bagaimanapun sejak IE ≅ IC, kami sampai pada persamaan berikut:

Perlu diingatkan bahawa dalam siri pengiraan yang kami buat dari Persamaan. (4.33) melalui Persamaan. (4.37) ,, elemen β tidak ada di mana-mana, dan IB belum dikira.

Ini menunjukkan bahawa titik-Q (seperti yang ditetapkan oleh I CQ dan V CEQ ) akibatnya tidak bergantung pada nilai β

Contoh Praktikal (4.8):

Mari kita gunakan analisis pada yang lebih awal Rajah 4.31 , menggunakan pendekatan perkiraan, dan membandingkan penyelesaian untuk ICQ dan VCEQ.

Di sini kita melihat bahawa tahap VB sama dengan ETh, seperti yang dinilai dalam contoh 4.7 kita sebelumnya. Apa maksudnya pada dasarnya adalah, perbezaan antara analisis anggaran dan analisis tepat dipengaruhi oleh RTh, yang bertanggungjawab untuk memisahkan ETh dan VB dalam analisis tepat.

Melangkah ke hadapan,

Contoh Seterusnya 4.9

Mari kita lakukan analisis tepat Contoh 4.7 jika β diturunkan menjadi 70, dan cari perbezaan antara penyelesaian untuk ICQ dan VCEQ.

Penyelesaian

Contoh ini tidak boleh diambil sebagai perbandingan antara strategi tepat berbanding perkiraan sebaliknya hanya untuk menguji tahap titik Q boleh bergerak sekiranya magnitud β dikurangkan sebanyak 50%. RTh dan ETh diberikan sama:

Menyusun hasil dalam bentuk jadual memberi kita perkara berikut:

Dari jadual di atas kita dapat mengetahui dengan jelas bahawa litar relatif tidak bertindak balas terhadap perubahan tahap β. Walaupun fakta bahawa magnitud β telah dikurangkan dengan ketara sebanyak 50%, dari nilai 140 hingga 70, walaupun nilai ICQ dan VCEQ pada dasarnya sama.

Contoh Seterusnya 4.10

Nilaikan tahap I CQ dan V CEQ untuk rangkaian pembahagi voltan seperti yang ditunjukkan dalam Rajah 4.33 dengan menerapkan tepat dan anggaran pendekatan dan membandingkan penyelesaian yang dihasilkan.

Dalam senario sekarang, syarat-syarat yang diberikan dalam Persamaan. (4.33) mungkin tidak berpuas hati, namun jawapannya dapat membantu kita mengenal pasti perbezaan penyelesaian dengan syarat Persamaan. (4.33) tidak diambil kira.

Rajah 4.33 Pembahagi voltan rangkaian untuk Contoh 4.10.

Menyelesaikan menggunakan Analisis Tepat:

Menyelesaikan menggunakan Analisis Perkiraan:

Dari penilaian di atas kita dapat melihat perbezaan antara hasil yang dicapai dari kaedah tepat dan anggaran.

Hasil kajian menunjukkan bahawa saya CQ sekitar 30% lebih tinggi untuk kaedah anggaran, sementara V CEQ adalah 10% lebih rendah. Walaupun hasilnya tidak sama, mengingat fakta bahawa βRE hanya 3 kali lebih besar daripada R2, hasilnya sebenarnya tidak terlalu terpisah.

Oleh itu, untuk analisis masa depan kita akan bergantung pada Persamaan. (4.33) untuk memastikan kesamaan maksimum antara kedua-dua analisis.

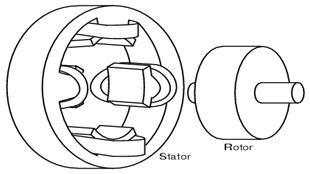

Sebelumnya: Litar Bias BJT yang stabil Seterusnya: Bipolar Junction Transistor (BJT) - Butiran Pembinaan, dan Operasi