Secara amnya, pengurang penuh adalah salah satu yang paling banyak digunakan dan litar logik gabungan penting . Ia adalah alat elektronik asas, digunakan untuk melakukan pengurangan dua nombor binari. Dalam artikel sebelumnya, kita sudah memberikan teori asas mengenai setengah penambah & penambah penuh yang menggunakan digit binari untuk pengiraan. Begitu juga, penolak penuh menggunakan digit binari seperti 0,1 untuk penolakan. Litar ini boleh dibina dengan pintu logik seperti pintu OR, Ex-OR, NAND. Input pengurang ini adalah A, B, Bin dan outputnya adalah D, Bout.

Artikel ini memberikan idea teori subtraktor penuh yang merangkumi premis seperti subtraktor, reka bentuk dengan gerbang logik, jadual kebenaran, dll. Artikel ini berguna untuk pelajar kejuruteraan yang dapat melalui topik ini di makmal Praktikal HDL.

Apa itu Subtraktor?

Pengurangan digit binari boleh dilakukan dengan bantuan litar subtraktor. Ini adalah salah satu jenis litar logik gabungan, yang digunakan untuk melakukan pengurangan dua digit binari seperti 0s dan 1s. Pengurangan digit binari dari 0 hingga 0 atau 0 hingga 1 tidak mengubah hasilnya, pengurangan 1 hingga 1 akan menghasilkan 0, tetapi pengurangan 1 hingga 0 perlu dipinjam.

Sebagai contoh, litar pengurangan dua bit merangkumi dua input seperti A & B sedangkan outputnya berbeza dan meminjam. Litar ini boleh dibina dengan penambah bersama dengan penyongsang yang terletak di antara setiap input data serta meminjam (Bin) input fasa awal FA.

Subtraktor dikelaskan kepada dua jenis seperti subtractor separuh dan subtraktor penuh. Di sini kita membincangkan pengurangan penuh.

Apa itu Penolak Penuh?

Ia adalah alat elektronik atau litar logik yang melakukan penolakan dua digit binari. Ini adalah rangkaian logik gabungan yang digunakan dalam elektronik digital. Banyak litar kombinasi boleh didapati di teknologi litar bersepadu iaitu penambah, pengekod, penyahkod, dan multiplexer. Dalam artikel ini, kita akan membincangkan pembinaannya menggunakan setengah pengurang dan juga istilah seperti jadual kebenaran.

Penolak Penuh

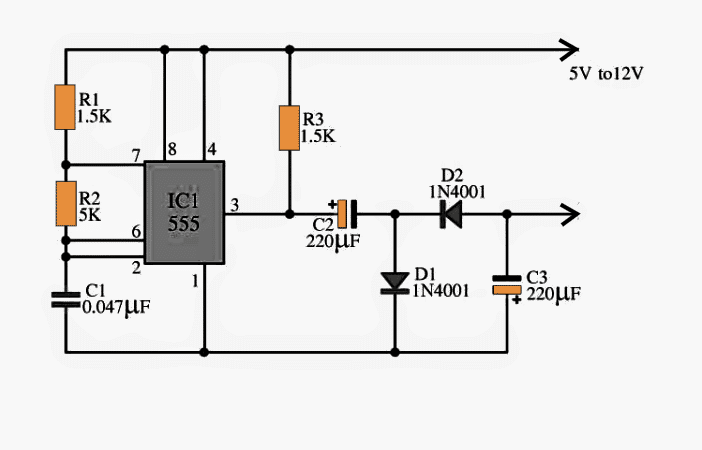

Perancangan ini dapat dilakukan oleh dua setengah pengurang, yang melibatkan tiga input seperti minuend, subtrahend, dan loan, meminjam bit antara input diperoleh dari pengurangan dua digit binari dan dikurangkan dari pasangan pesanan tinggi seterusnya bit, output sebagai perbezaan dan pinjam.

The gambarajah blok penolak penuh ditunjukkan di bawah. Kelemahan utama bagi pengurang separuh ialah, kita tidak dapat membuat sedikit Pinjaman dalam pengurang ini. Walaupun dalam reka bentuknya, sebenarnya kita dapat membuat sedikit Pinjaman di litar & dapat mengurangkan dengan baki dua i / ps. Di sini A adalah minuend, B adalah subtrahend & Bin dipinjam. Hasilnya adalah Perbezaan (Diff) & Bout (Pinjam keluar). Litar subtraktor lengkap dapat diperoleh dengan menggunakan dua subtraktor setengah dengan gerbang OR tambahan.

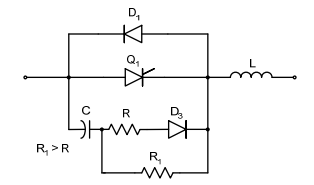

Diagram Litar Subtraktor Penuh dengan Gerbang Logik

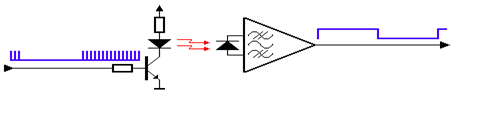

The gambarajah litar penolak penuh menggunakan gerbang asas s ditunjukkan dalam gambarajah blok berikut. Litar ini boleh dilakukan dengan dua litar separuh Pengurangan.

Dalam litar separuh Subtraktor awal, input binari adalah A dan B. Seperti yang telah kita bincangkan dalam artikel setengah Subtraktor sebelumnya, ia akan menghasilkan dua output iaitu perbezaan (Diff) & Borrow.

Penolak Penuh menggunakan Logic Gates

Perbezaan o / p subtraktor kiri diberikan kepada litar Kurang separuh Kurang. Output Diff seterusnya diberikan kepada input litar Subtraktor separuh kanan. Kami menawarkan Pinjaman sedikit demi sedikit di i / p seterusnya litar separuh pengurangan . Sekali lagi ia akan memberi Diff keluar dan juga meminjam sedikit. Output akhir pengurang ini adalah Diff-output.

Sebaliknya, pinjaman dari kedua-dua litar Subtraktor disambungkan ke pintu logik ATAU. Kemudian daripada memberikan logik ATAU untuk dua bit keluaran subtraktor, kami memperoleh Pinjaman akhir dari pengurang. Pinjaman terakhir untuk menandakan MSB (bit yang paling ketara).

Sekiranya kita melihat litar dalaman ini, kita dapat melihat dua Setengah Pengurang dengan gerbang NAND dan gerbang XOR dengan gerbang ATAU tambahan.

Jadual Kebenaran Penolak Penuh

Ini litar penolak melaksanakan pengurangan antara dua bit, yang mempunyai 3- input (A, B, dan Bin) dan dua output (D dan Bout). Di sini input menunjukkan minuend, subtrahend, & loan sebelumnya, sedangkan kedua output tersebut dilambangkan sebagai pinjaman o / p dan selisih. Gambar berikut menunjukkan jadual kebenaran penolak penuh.

Input | Keluaran | |||

Minuend (A) | Subtrahend (B) | Pinjam (Bin) | Perbezaan (D) | Pinjam (Pertarungan) |

0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

Peta K

Penyederhanaan K-peta penolak penuh untuk perbezaan dan pinjaman di atas ditunjukkan di bawah.

Persamaan perbezaan dan Bin disebutkan di bawah.

Ungkapan untuk Perbezaan adalah,

D = A'B'Bin + AB'Bin '+ A'BBin' + ABBin

Ungkapan untuk Borrow adalah,

Bout = A'Bin + A'B + BBin

Melambung Litar Subtraktor Penuh

Sebelum ini, kami telah membincangkan gambaran keseluruhan pembinaan seperti ini, rajah litar dengan pintu logik. Tetapi jika kita ingin mengurangkan dua nombor 1-bit yang lebih banyak, litar penolak ini sangat membantu untuk melonjakkan nombor bit tunggal dan juga mengurangkan lebih daripada dua nombor perduaan. Dalam kes seperti itu, litar lata bertingkat digunakan dengan bantuan pintu logik TIDAK. Penukaran litar dari penambah penuh ke penolak penuh dapat dilakukan dengan menggunakan teknik pelengkap 2.

Secara amnya, alihkan input subtrahend untuk penambah penuh menggunakan pintu Gerbang sebaliknya penyongsang. Dengan menambahkan Minuend (input tidak terbalik) & Subtrahend (Inverted Input) ini, LSB (input input) litar FA adalah 1, yang bermaksud Logik Tinggi jika tidak, kita tolak dua digit binari menggunakan teknik pelengkap 2. Keluaran FA adalah bit Diff & jika kita membalikkan pelaksanaan maka kita boleh mendapatkan MSB sebaliknya Borrow bit. Sebenarnya, kita dapat merancang litar supaya output dapat diperhatikan.

Kod Verilog

Untuk bahagian pengekodan, pertama, kita perlu memeriksa cara pemodelan struktur rajah litar logik. Gambarajah logik ini boleh dibina menggunakan gerbang AND, litar separuh pengurang, dan gabungan gerbang logik seperti gerbang AND, OR, NOT, XOR. Seperti dalam pemodelan struktur, kami menerangkan pelbagai modul untuk setiap susunan elemen asas. Dalam kod berikut, modul yang berbeza dapat ditentukan untuk setiap gerbang.

Modul ini adalah untuk pintu OR.

INPUT: a0, b0

HASIL: c0

Terakhir, kami akan menyatukan modul tepat gerbang ini menjadi satu-satunya modul. Untuk itu, di sini kita menggunakan contoh modul. Sekarang contoh ini dapat digunakan setelah kita ingin meniru modul atau fungsi yang tepat untuk pelbagai set input. Mula-mula, kita merancang pengurang separuh kemudian modul ini digunakan untuk melaksanakan penolak penuh. Untuk melaksanakannya, kami menggunakan gerbang OR untuk menggabungkan o / ps untuk pemboleh ubah Bout. The kod verilog untuk penolak penuh ditunjukkan di bawah

modul atau_gate (a0, b0, c0)

masukan a0, b0

keluaran c0

berikan c0 = a0 | b0

endmodul

modul xor_gate (a1, b1, c1)

input a1, b1

output c1

berikan c1 = a1 ^ b1

endmodul

modul dan_gate (a2, b2, c2)

masukan a2, b2

output c2

tetapkan c2 = a2 & b2

endmodul

modul not_gate (a3, b3)

input a3

keluaran b3

berikan b3 = ~ a3

endmodul

modul_subtractor (a4, b4, c4, d4)

masukan a4, b4

output c4, d4

wayar x

xor_gate u1 (a4, b4, c4)

dan_gate u2 (x, b4, d4)

not_gate u3 (a4, x)

endmodul

modul full_subtractor (A, B, Bin, D, Bout)

input A, B, Bin

keluaran D, Bout

wayar p, q, r

half_subtractor u4 (A, B, p, q)

half_subtractor u5 (p, Bin, D, r)

atau_gate u6 (q, r, Bout)

endmodul

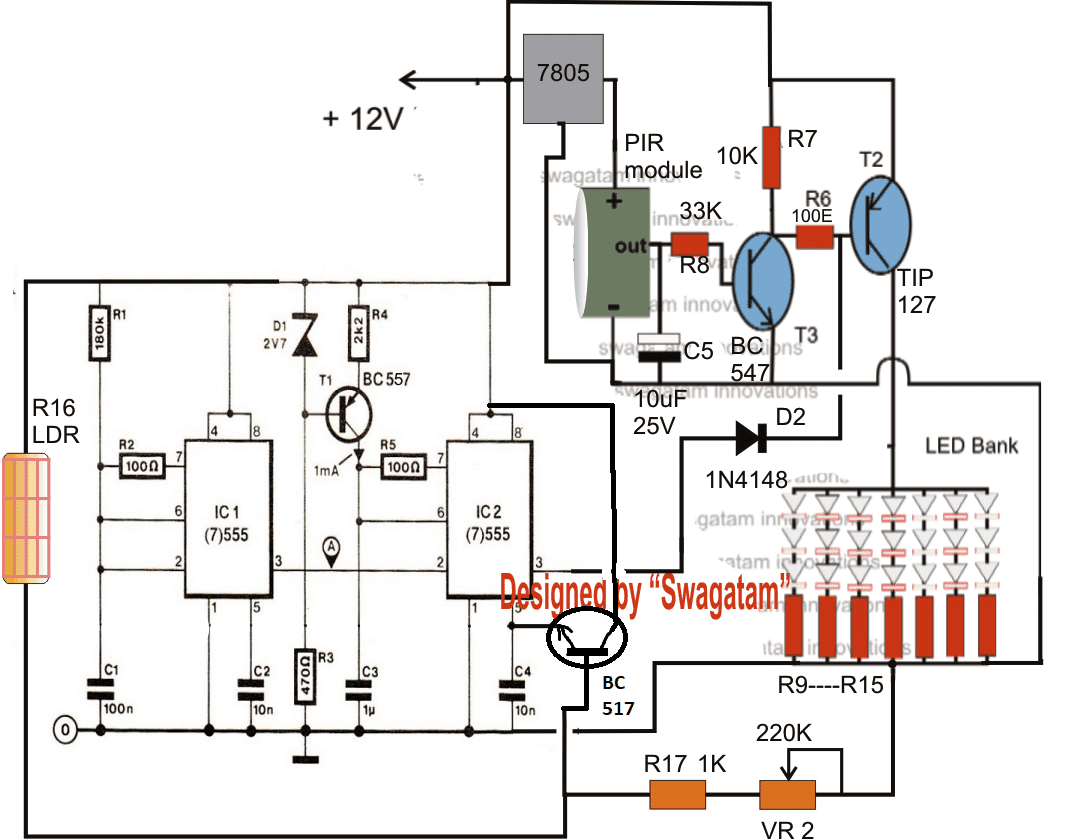

Penolak Penuh menggunakan Multiplexer 4X1

Pelaksanaan pengurangan boleh dilakukan melalui kaedah pelengkap kedua-duanya. Oleh itu, kami memerlukan penggunaan gerbang 1-XOR yang digunakan untuk membalikkan 1-bit & memasukkannya ke dalam bit bawa. Keluaran PERBEZAAN serupa dengan keluaran SUM di litar penambah penuh namun BARROW o / p tidak serupa dengan keluaran pembawa penambah penuh namun ia terbalik dan juga dipuji, seperti A - B = A + (-B) = A + dua pelengkap B.

Reka bentuk ini menggunakan multiplexer 4X1 ditunjukkan dalam rajah logik berikut. Reka bentuk ini boleh dilakukan dengan menggunakan langkah-langkah berikut.

Multiplexer 4X1

- Pada langkah 1, terdapat dua output seperti Sub dan Borrow. Oleh itu, kita harus memilih 2 multiplexer.

- Pada langkah2, jadual kebenaran dapat dilaksanakan bersama dengan peta K

- Pada langkah3, dua pemboleh ubah boleh dipilih sebagai garis pilihan anda. Contohnya, B & C dalam kes ini.

Jadual Kebenaran

The jadual kebenaran penolak penuh litar menggunakan multiplexer 4X1 merangkumi yang berikut

KE | B | C | Sub | Pinjam |

0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

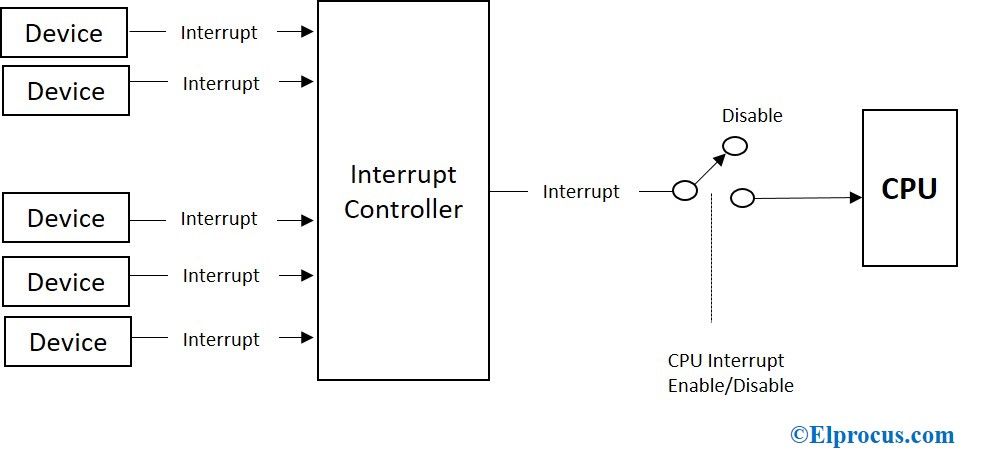

Penolak Penuh menggunakan Decoder

Perancangan subtraktor penuh menggunakan 3-8 penyahkod dapat dilakukan dengan menggunakan output rendah aktif. Mari kita anggap penyahkod berfungsi dengan menggunakan rajah logik berikut. Decoder merangkumi tiga input dalam 3-8 decoder. Berdasarkan jadual kebenaran, kita dapat menulis minterms untuk output perbezaan & meminjam.

Dari jadual kebenaran di atas,

Untuk fungsi yang berbeza dalam jadual kebenaran, minterms boleh ditulis sebagai 1,2,4,7, dan juga, untuk pinjaman, minterms boleh ditulis sebagai 1,2,3,7. Decoder 3-8 merangkumi tiga input serta 8 output seperti angka0 hingga 7.

Penyahkod 3 hingga 8

Sekiranya input penolak adalah 000, maka output ‘0’ akan aktif dan jika inputnya 001, maka output ‘1’ akan aktif.

Sekarang output pengurang boleh diambil dari 1, 2, 4 & 7 untuk menghubungkannya ke gerbang NAND, maka outputnya akan menjadi perbezaannya. Output ini boleh dihubungkan ke gerbang logik NAND lain di mana output berubah menjadi pinjaman.

Sebagai contoh, jika input adalah 001, maka outputnya adalah 1 yang bermaksud aktif. Jadi output aktif rendah dan output dapat diperoleh dari gerbang NAND yang disebut fungsi perbezaan seperti tinggi dan fungsi meminjam juga berubah menjadi tinggi. Oleh itu kita mendapat output pilihan. Jadi akhirnya, penyahkod berfungsi seperti penolak penuh.

Kelebihan dan kekurangan

The kelebihan penolak sertakan perkara berikut.

- Perancangan subtraktor sangat mudah dan boleh dilaksanakan

- Pemotongan kuasa dalam DSP (pemprosesan isyarat digital)

- Tugas komputasi dapat dijalankan dengan kelajuan tinggi.

The kelemahan penolak sertakan perkara berikut.

- Pada subtraktor separuh, tidak ada syarat untuk menerima input seperti Pinjaman dari fasa sebelumnya.

- Kelajuan pengurang boleh menjadi separa melalui kelewatan litar.

Permohonan

Sesetengah aplikasi subtraktor penuh sertakan perkara berikut

- Ini umumnya digunakan untuk ALU (Aritmetik logic unit) dalam komputer untuk mengurangkan sebagai CPU & GPU untuk aplikasi grafik untuk mengurangkan kesukaran litar.

- Subtraktor banyak digunakan untuk melakukan fungsi aritmetik seperti pengurangan, dalam kalkulator elektronik dan juga peranti digital.

- Ini juga berlaku untuk mikrokontroler yang berbeza untuk pengurangan aritmetik, pemasa, dan kaunter program (PC)

- Subtraktor digunakan dalam prosesor untuk menghitung jadual, alamat, dll.

- Ia juga berguna untuk DSP dan sistem berasaskan rangkaian.

- Ini digunakan terutamanya untuk ALU dalam komputer untuk mengurangkan seperti CPU & GPU untuk aplikasi grafik untuk mengurangkan kerumitan rangkaian.

- Ini terutamanya digunakan untuk melakukan fungsi aritmetik seperti pengurangan dalam peranti digital, kalkulator, dll.

- Pengurang ini juga sesuai untuk pelbagai mikrokontroler untuk pemasa, PC (kaunter program) & pengurangan aritmetik

- Ini digunakan untuk pemproses untuk mengira alamat, jadual, dll.

- Pelaksanaan ini dengan gerbang logik seperti NAND & NOR boleh dilakukan dengan litar logik subtraktor penuh kerana kedua-dua gerbang NOR & NAND disebut sebagai gerbang sejagat.

Dari maklumat di atas, dengan menilai penambah, penolak penuh menggunakan dua litar subtraktor, dan bentuk tabularnya, seseorang dapat melihat bahawa Dout dalam penolak penuh sama dengan Sout penambah penuh. Satu-satunya variasi adalah bahawa A (pemboleh ubah input) dilengkapi dengan subtraktor penuh. Oleh itu, dapat dicapai untuk menukar litar penambah penuh menjadi penolak penuh dengan hanya melengkapkan i / p A sebelum diberikan kepada gerbang logik untuk menghasilkan output pinjaman-bit terakhir (Bout).

Dengan menggunakan litar logik subtraktor penuh, subtraktor penuh menggunakan gerbang NAND dan gerbang atau pengurang subtraktor penuh dapat dilaksanakan, kerana kedua-dua gerbang NAND dan NOR dianggap sebagai gerbang sejagat. Berikut adalah soalan untuk anda, apakah perbezaan antara subtraktor separuh dan subtraktor penuh?