Fungsi utama penjana pariti dan pemeriksa pariti adalah untuk mengesan kesilapan dalam penghantaran data dan konsep ini diperkenalkan pada tahun 1922. Dalam teknologi RAID, bit paritas dan pemeriksa pariti digunakan untuk melindungi daripada kehilangan data. Bit paritas adalah bit tambahan yang disetkan di sisi transmisi ke ‘0’ atau ‘1’, ia digunakan untuk mengesan hanya ralat bit tunggal dan ia adalah kaedah paling mudah untuk mengesan kesalahan. Terdapat pelbagai jenis kod pengesanan ralat yang digunakan untuk mengesan kesalahan seperti parity, ring counter, block parity code, Hamming code, biquinary, dll. Penjelasan ringkas mengenai parity bit, parity penjana dan pemeriksa dijelaskan di bawah.

Apa itu Parity Bit?

Definisi: Bit paritas atau bit periksa adalah bit yang ditambahkan pada kod binari untuk memeriksa sama ada kod tertentu sama atau tidak, misalnya, sama ada kod itu sama rata atau pariti ganjil diperiksa oleh bit periksa ini atau bit pariti. Paritas tidak lain adalah bilangan 1 dan terdapat dua jenis bit pariti iaitu bit sedikit dan ganjil.

Dalam bit pariti ganjil, kodnya mestilah dalam bilangan ganjil 1, misalnya, kita mengambil kod 5-bit 100011, kod ini dikatakan pariti ganjil kerana terdapat tiga nombor 1 dalam kod yang telah kita ambil . Dalam bit genap, kod mestilah dalam bilangan genap 1, misalnya, kita mengambil kod 610 bit 101101, kod ini dikatakan sama rata kerana terdapat empat nombor 1 dalam kod yang telah kita ambil

Apakah Penjana Pariti?

Definisi: Penjana pariti adalah rangkaian kombinasi pada pemancar, ia mengambil mesej asal sebagai input dan menghasilkan bit pariti untuk mesej itu dan pemancar dalam penjana ini menghantar mesej bersama dengan bit paritasnya.

Jenis Penjana Pariti

Pengelasan penjana ini ditunjukkan dalam rajah di bawah

jenis-of-parity-generator

Malah Penjana Pariti

Penjana pariti genap mengekalkan data binari dalam bilangan genap 1's, sebagai contoh, data yang diambil adalah bilangan ganjil 1, penjana pariti genap ini akan mengekalkan data sebagai bilangan genap 1 dengan menambahkan 1 tambahan ke ganjil bilangan 1. Ini juga merupakan rangkaian gabungan yang outputnya bergantung pada data input yang diberikan, yang bermaksud data input adalah data binari atau kod binari yang diberikan untuk penjana pariti.

Mari kita pertimbangkan tiga data binari input, bahawa tiga bit dianggap sebagai A, B, dan C. Kita boleh menulis 23gabungan menggunakan tiga data binari input iaitu dari 000 hingga 111 (0 hingga 7), jumlah lapan kombinasi akan diperoleh dari tiga data binari input yang telah kita pertimbangkan. Jadual kebenaran penjana pariti genap untuk tiga data binari input ditunjukkan di bawah.

0 0 0 - Dalam kod binari input ini, paritas genap diambil sebagai '0' kerana input sudah sama rata, jadi tidak perlu menambahkan pariti genap sekali lagi untuk input ini.

0 0 1 - - Dalam kod binari input ini hanya terdapat satu nombor ‘1’ dan satu nombor ‘1’ itu adalah nombor ganjil ‘1’. Sekiranya terdapat nombor ganjil ‘1’, maka penjana pariti mesti menghasilkan ‘1’ yang lain untuk menjadikannya sama rata, jadi paritas sama diambil sebagai 1 untuk menjadikan kod 0 0 1 menjadi pariti.

0 1 0 - Bit ini berada dalam pariti ganjil sehingga paritas genap diambil sebagai 1 untuk menjadikan kod 0 1 0 menjadi pariti genap.

0 1 1 - Bit ini sudah sama rata sehingga pariti sama diambil sebagai 0 untuk menjadikan kod 0 1 1 menjadi pariti genap.

1 0 0 - Bit ini berada dalam pariti ganjil sehingga paritas genap diambil sebagai 1 untuk menjadikan kod 1 0 0 menjadi pariti genap.

1 0 1 - Bit ini sudah sama rata sehingga pariti sama diambil sebagai 0 untuk menjadikan kod 1 0 1 menjadi pariti genap.

1 1 0 - Bit ini juga sama rata sehingga pariti sama diambil sebagai 0 untuk menjadikan kod 1 1 0 menjadi pariti genap.

1 1 1 - Bit ini berada dalam pariti ganjil sehingga paritas genap diambil sebagai 1 untuk menjadikan kod 1 1 1 menjadi pariti genap.

Jadual Kebenaran Penjana Pariti

| A B C | Malah Pariti |

| 0 0 0 | 0 |

| 0 0 1 | 1 |

| 0 1 0 | 1 |

| 0 1 1 | 0 |

| 1 0 0 | 1 |

| 1 0 1 | 0 |

| 1 1 0 | 0 |

| 1 1 1 | 1 |

Penyederhanaan peta karnaugh (k-map) untuk input tiga bit sama rata

k-peta-untuk-walaupun-pariti-penjana

Dari jadual kebenaran pariti di atas, ungkapan kesederhanaan pariti ditulis sebagai

Ungkapan keseimbangan genap yang dilaksanakan dengan menggunakan dua gerbang Ex-OR dan rajah logik kesamaan ini menggunakan Ex-OR pintu logik ditunjukkan di bawah.

litar genap-pariti-logik

Dengan cara ini, penjana pariti merata menghasilkan nombor 1 genap dengan mengambil data input.

Penjana Pariti Ganjil

Penjana pariti ganjil mengekalkan data binari dalam bilangan ganjil 1, misalnya, data yang diambil adalah dalam bilangan genap 1's, penjana pariti ganjil ini akan mengekalkan data sebagai nombor ganjil 1 dengan menambahkan tambahan 1 hingga 1 bilangan genap 1's. Ini adalah rangkaian gabungan yang outputnya selalu bergantung pada data input yang diberikan. Sekiranya terdapat bilangan genap 1, maka hanya sedikit pariti ditambahkan untuk menjadikan kod binari menjadi nombor ganjil 1.

Mari kita pertimbangkan tiga data binari input, bahawa tiga bit dianggap sebagai A, B, dan C. Jadual kebenaran penjana pariti ganjil untuk tiga data binari input ditunjukkan di bawah.

0 0 0 - Dalam kod binari input ini, pariti ganjil diambil sebagai '1' kerana inputnya sama rata.

0 0 1 - Input binari ini sudah berada dalam pariti ganjil, jadi pariti ganjil diambil sebagai 0.

0 1 0 - Input binari ini juga dalam pariti ganjil, jadi pariti ganjil diambil sebagai 0.

0 1 1 - Bit ini sama rata sehingga pariti ganjil diambil sebagai 1 untuk menjadikan kod 0 1 1 menjadi pariti ganjil.

1 0 0 - Bit ini sudah berada dalam pariti ganjil, jadi pariti ganjil diambil sebagai 0 untuk menjadikan kod 1 0 0 menjadi pariti ganjil.

1 0 1 - Bit input ini sama rata, jadi pariti ganjil diambil sebagai 1 untuk menjadikan kod 1 0 1 menjadi pariti ganjil.

1 1 0 - Bit ini sama rata, jadi pariti ganjil diambil sebagai 1.

1 1 1 - Bit input ini berada dalam pariti ganjil, jadi pariti ganjil diambil sebagai o.

Jadual Kebenaran Penjana Pariti Ganjil

| A B C | Pariti Ganjil |

| 0 0 0 | 1 |

| 0 0 1 | 0 |

| 0 1 0 | 0 |

| 0 1 1 | 1 |

| 1 0 0 | 0 |

| 1 0 1 | 1 |

| 1 1 0 | 1 |

| 1 1 1 | 0 |

Penyederhanaan peta Kavanaugh (k-map) untuk keseimbangan input tiga bit adalah

k-peta-untuk-ganjil-pariti-penjana

Dari jadual kebenaran pariti ganjil di atas, ungkapan kesederhanaan parity bit ditulis sebagai

Gambarajah logik penjana pariti ganjil ini ditunjukkan di bawah.

litar logik

Dengan cara ini, penjana pariti ganjil menghasilkan nombor ganjil 1 dengan mengambil data input.

Apa itu Parity Check?

Definisi: Litar gabungan di penerima adalah pemeriksa pariti. Pemeriksa ini mengambil mesej yang diterima termasuk bit pariti sebagai input. Ia memberikan output '1' jika terdapat beberapa ralat yang dijumpai dan memberikan output '0' jika tidak terdapat ralat dalam mesej termasuk bit pariti.

Jenis Pemeriksa Pariti

Klasifikasi pemeriksa pariti ditunjukkan dalam gambar di bawah

jenis-pemeriksa-pariti

Pemeriksa Pariti Malah

Dalam pemeriksa pariti sama ada bit ralat (E) sama dengan '1', maka kita mempunyai ralat. Sekiranya bit ralat E = 0 maka menunjukkan tidak ada kesalahan.

Error Bit (E) = 1, ralat berlaku

Ralat Bit (E) = 0, tiada ralat

Litar pemeriksa pariti ditunjukkan dalam rajah di bawah

litar logik

Pemeriksa Pariti Ganjil

Dalam pemeriksa pariti ganjil jika bit ralat (E) sama dengan '1', maka ini menunjukkan tidak ada ralat. Sekiranya bit ralat E = 0 maka menunjukkan ada ralat.

Ralat Bit (E) = 1, tiada ralat

Kesalahan Bit (E) = 0, ralat berlaku

Pemeriksa pariti tidak akan dapat mengesan jika terdapat kesilapan pada bit lebih dari ‘1’ dan data yang betul juga tidak mungkin dilakukan, ini adalah kelemahan utama pemeriksa pariti.

Parity Generator / Checker menggunakan IC

IC 74180 melakukan fungsi penjanaan pariti dan juga pemeriksaan. Penjana / Pemeriksa Pariti 9 bit (8 bit data, 1 bit pariti) ditunjukkan dalam rajah di bawah.

ic-74180

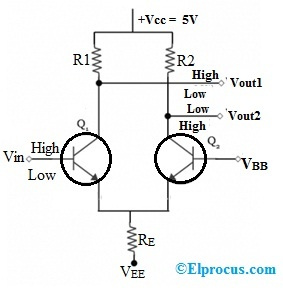

IC 74180 mengandungi lapan bit data (X0hingga X7), VDC,input genap, input ganjil, Tujuh output, output S ganjil, dan pin tanah.

Sekiranya input genap dan ganjil yang diberikan keduanya tinggi (H), maka output genap dan ganjil keduanya rendah (L), sama, jika input yang diberikan keduanya Rendah (L), maka output genap dan ganjil keduanya menjadi tinggi ( H).

Kelebihan Parity

Kelebihan pariti adalah

- Kesederhanaan

- Mudah untuk digunakan

Permohonan Pariti

Aplikasi pariti adalah

- Dalam sistem digital dan banyak aplikasi perkakasan, pariti ini digunakan

- Bit paritas juga digunakan dalam Antaramuka Sistem Komputer Kecil (SCSI) dan juga dalam Perisian Komponen Perisian (PCI) untuk mengesan ralat

Soalan Lazim

1). Apakah perbezaan antara penjana pariti dan pemeriksa pariti?

Penjana pariti menghasilkan bit pariti dalam pemancar dan pemeriksa pariti memeriksa bit pariti di penerima.

2). Apa maksud pariti tidak?

Apabila bit pariti tidak digunakan untuk memeriksa kesilapan maka bit pariti dikatakan tidak parity atau tidak ada parity atau ketiadaan parity.

3). Berapakah nilai pariti?

Konsep nilai pariti yang digunakan untuk kedua-dua komoditi dan sekuriti dan istilah merujuk kepada apabila nilai kedua-dua aset itu sama.

4). Mengapa kita memerlukan pemeriksa pariti?

Pemeriksa pariti diperlukan untuk mengesan kesalahan dalam komunikasi dan juga dalam peranti penyimpanan memori pemeriksa pariti digunakan untuk pengujian.

5). Bagaimana bit paritas dapat mengesan unit data yang rosak?

Bit berlebihan dalam teknik ini disebut bit pariti, ia mengesan unit data yang rosak apabila berlaku ralat semasa penghantaran data.

Dalam artikel ini, bagaimana kesamarataan penjana dan pemeriksa menghasilkan dan memeriksa bit dan jenisnya, litar logik, jadual kebenaran, dan ungkapan k-peta dibincangkan secara ringkas. Inilah soalan untuk anda, bagaimana anda mengira paritas genap dan ganjil?