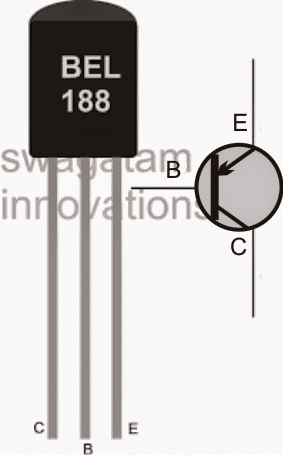

Walaupun transistor (BJT) banyak digunakan untuk membuat litar penguat, ini juga dapat digunakan dengan berkesan untuk menukar aplikasi.

Suis transistor adalah litar di mana pengumpul transistor dihidupkan / dimatikan dengan arus yang lebih besar sebagai tindak balas kepada isyarat ON / OFF arus rendah yang sesuai pada pemancar asasnya.

Sebagai contoh, berikut Konfigurasi BJT boleh digunakan sebagai suis kerana membalikkan isyarat input untuk litar logik komputer.

Di sini anda dapati bahawa voltan keluaran Vc bertentangan dengan potensi yang digunakan di dasar / pemancar transistor.

Juga, pangkalannya tidak dihubungkan dengan sumber DC tetap, tidak seperti litar berasaskan penguat. Pengumpul mempunyai sumber DC yang sesuai dengan tahap bekalan sistem, misalnya 5 V dan 0 V dalam casing aplikasi komputer ini.

Kami akan membincangkan bagaimana penyongsangan voltan ini dapat dirancang untuk memastikan bahawa titik operasi beralih dari pemotongan ke tepu dengan betul di sepanjang garis beban seperti yang ditunjukkan dalam gambar berikut:

Untuk senario sekarang, dalam gambar di atas kita telah menganggap bahawa IC = ICEO = 0 mA, ketika IB = 0 uA (pendekatan yang bagus untuk meningkatkan strategi pembinaan). Selain itu mari kita anggap bahawa VCE = VCE (sat) = 0 V, bukannya tahap 0.1 hingga 0.3 V yang biasa.

Sekarang, pada Vi = 5 V BJT akan dihidupkan, dan pertimbangan reka bentuk mesti memastikan bahawa konfigurasi sangat tepu, dengan magnitud IB yang mungkin lebih daripada nilai yang berkaitan dengan lengkung IB yang dilihat hampir dengan tahap tepu.

Seperti yang dapat dijelaskan dalam gambar di atas, syarat ini memerlukan IB lebih besar daripada 50 uA.

Mengira Tahap Ketepuan

Tahap tepu pemungut untuk litar yang ditunjukkan dapat dikira menggunakan formula:

IC (sat) = Vcc / Rc

Besarnya arus asas di rantau aktif sebelum tahap tepu dapat dikira menggunakan formula:

IB (maks) ≅ IC (sat) / βdc ---------- Persamaan 1

Ini menunjukkan bahawa, untuk melaksanakan tahap ketepuan, syarat berikut harus dipenuhi:

IB> IC (sat) / IC (sat) / βdc -------- Persamaan 2

Dalam grafik yang dibincangkan di atas, apabila Vi = 5 V, tahap IB yang dihasilkan dapat dinilai dengan kaedah berikut:

Sekiranya kita menguji persamaan 2 dengan hasil ini, kita dapat:

Ini nampaknya memenuhi syarat yang diperlukan. Tidak syak lagi, nilai IB yang lebih tinggi daripada 60 uA akan dibenarkan masuk melintasi titik Q di atas garis beban yang terletak sangat dekat dengan paksi menegak.

Sekarang, merujuk ke rangkaian BJT yang ditunjukkan dalam rajah pertama, sementara Vi = 0 V, IB = 0 uA, dan dengan asumsi IC = ICEO = 0 mA, penurunan voltan yang berlaku di seluruh RC akan seperti dalam formula:

VRC = ICRC = 0 V.

Ini memberi kita VC = +5 V untuk rajah pertama di atas.

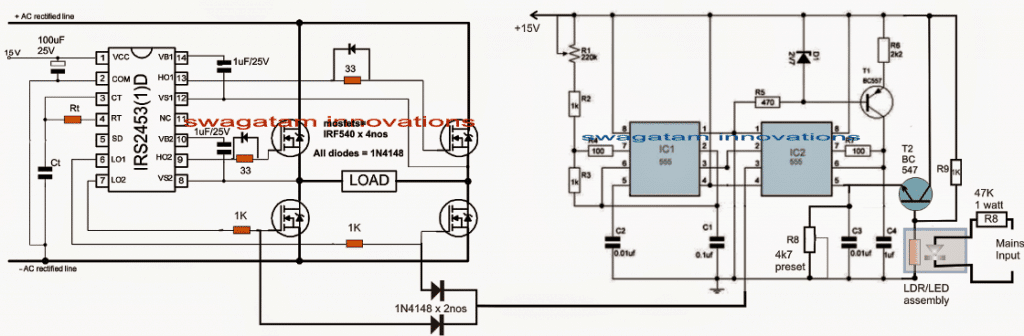

Selain aplikasi peralihan logoc komputer, konfigurasi BJT ini juga dapat dilaksanakan seperti suis menggunakan titik ekstrim sama dari garis beban.

Apabila ketepuan berlaku, IC semasa cenderung menjadi cukup tinggi, yang sesuai menurunkan voltan VCE ke titik terendah.

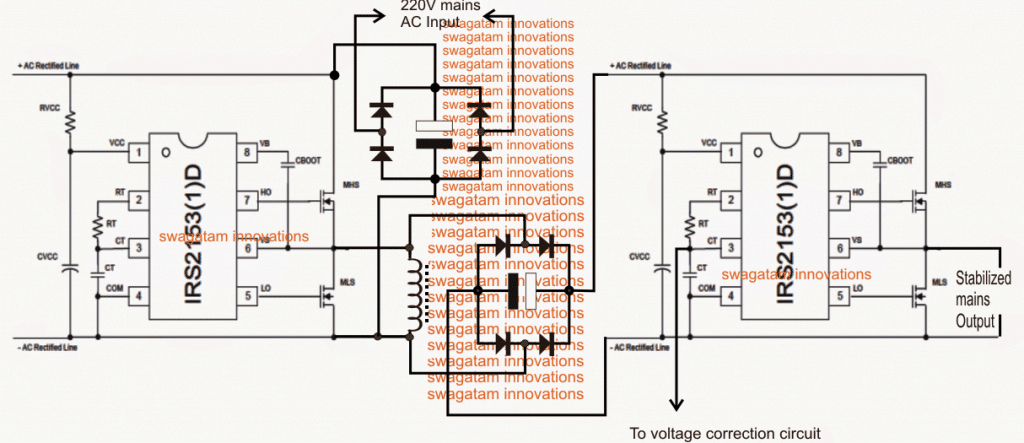

Ini menimbulkan tahap rintangan di kedua terminal seperti yang digambarkan dalam gambar berikut dan dikira menggunakan formula berikut:

R (sat) = VCE (sat) / IC (sat) seperti yang ditunjukkan pada gambar berikut.

Sekiranya kita menganggap nilai purata biasa untuk VCE (sat) seperti 0.15 V dalam formula di atas, kita mendapat:

Nilai rintangan di terminal pemancar pemungut ini kelihatan agak kecil jika dibandingkan dengan rintangan siri dalam kilo Ohms di terminal pemungut BJT.

Sekarang, apabila input Vi = 0 V, pengalihan BJT akan terputus menyebabkan rintangan di seluruh pemancar kolektor menjadi:

R (cutoff) = Vcc / ICEO = 5 V / 0 mA = ∞ Ω

Ini menimbulkan situasi litar terbuka di terminal pemancar pemungut. Sekiranya kita mempertimbangkan nilai tipikal 10 uA untuk ICEO, nilai rintangan pemotongan akan seperti di bawah:

Rcutoff = Vcc / ICEO = 5 V / 10 uA = 500 k Ω

Nilai ini kelihatan sangat besar dan setara dengan litar terbuka untuk kebanyakan konfigurasi BJT sebagai suis.

Menyelesaikan Contoh Praktikal

Hitung nilai RB dan RC untuk suis transistor yang dikonfigurasi seperti penyongsang di bawah, memandangkan ICmax = 10mA

Formula untuk menyatakan ketepuan pengumpul adalah:

ICsat = Vcc / Rc

∴ 10 mA = 10 V / Rc

∴ Rc = 10 V / 10 mA = 1 kΩ

Juga, pada titik tepu

IB ≅ IC (sat) / βdc = 10 mA / 250 = 40 μA

Untuk ketepuan terjamin, mari pilih IB = 60 μA, dan dengan menggunakan formula

IB = Vi - 0,7 V / RB, kita dapat

RB = 10 V - 0,7 V / 60 μA = 155 kΩ,

Membundarkan hasil di atas menjadi 150 kΩ, dan menilai formula di atas sekali lagi kita mendapat:

IB = Vi - 0,7 V / RB

= 10 V - 0,7 V / 150 kΩ = 62 μA,

sejak IB = 62 μA > ICsat / βdc = 40 μA

Ini mengesahkan bahawa kita harus menggunakan RB = 150 kΩ

Mengira Transistor Beralih

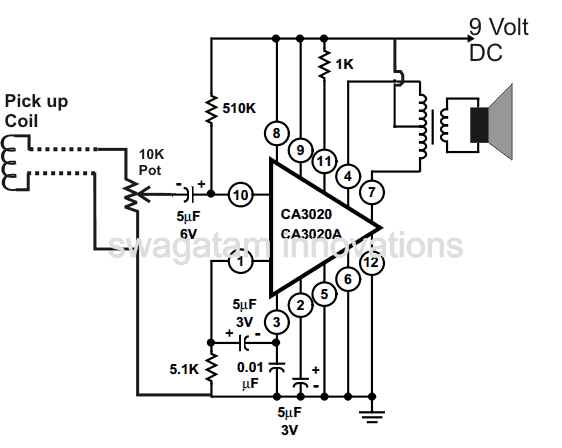

Anda akan menjumpai transistor khas yang disebut beralih transistor kerana kadar pantas mereka beralih dari satu tahap voltan ke tahap yang lain.

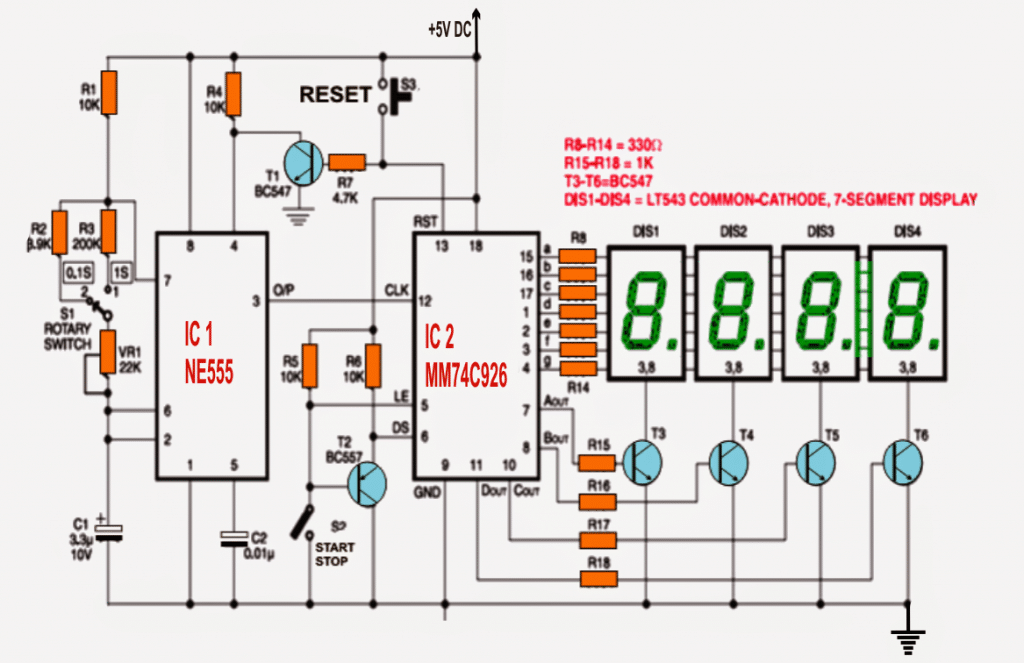

Rajah berikut membandingkan jangka masa yang dilambangkan sebagai ts, td, tr, dan tf dengan arus pemungut peranti.

Kesan jangka masa pada tindak balas kelajuan pengumpul ditentukan oleh tindak balas arus pemungut seperti yang ditunjukkan di bawah:

Jumlah masa yang diperlukan untuk transistor beralih dari keadaan 'mati' ke keadaan 'on' dilambangkan sebagai t (on) dan dapat ditentukan oleh formula:

t (on) = tr + td

Di sini td mengenal pasti kelewatan yang berlaku semasa isyarat pensuisan input berubah keadaan dan output transistor bertindak balas terhadap perubahan tersebut. Masa tr menunjukkan kelewatan pertukaran akhir dari 10% hingga 90%.

Jumlah masa yang diambil oleh bJt dari keadaan AKTIF ke keadaan MATI ditunjukkan sebagai t (mati), dan dinyatakan dengan formula:

t (mati) = ts + tf

ts menentukan masa penyimpanan, sementara tf mengenal pasti masa jatuh dari 90% hingga 10% dari nilai asal.

Rujuk pada grafik di atas, untuk tujuan umum BJT, jika arus pengumpul Ic = 10 mA, kita dapat melihat bahawa:

ts = 120 ns, td = 25 ns, tr = 13 ns, tf = 12 ns

yang bermaksud t (on) = tr + td = 13 ns + 25 ns = 38 ns

t (mati) = ts + tf = 120 ns + 12 ns = 132 ns

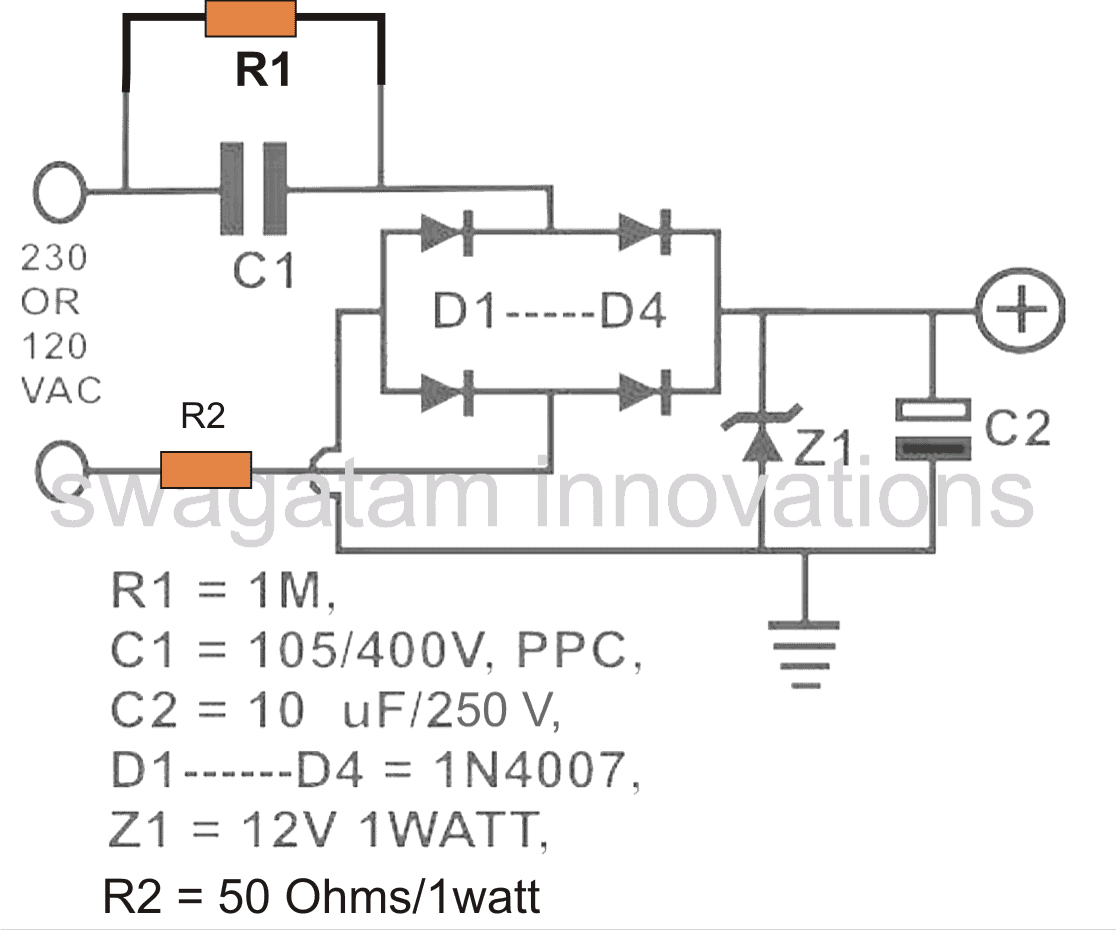

Sebelumnya: Cara Membuat PCB di Rumah Seterusnya: Litar Diod Zener, Karakteristik, Pengiraan