Dalam siaran ini kita akan belajar cara membina get logik NOT, AND, NAND, OR, dan NOR menggunakan transistor diskret. Kelebihan utama menggunakan get logik transistor ialah ia boleh berfungsi walaupun dengan voltan serendah 1.5 V.

Dalam sesetengah aplikasi elektronik, voltan yang tersedia mungkin tidak mencukupi untuk menghidupkan IC TTL atau CMOS. Ini benar terutamanya untuk alat yang menggunakan bateri. Tidak syak lagi, anda sentiasa mempunyai pilihan IC logik 3 volt. Walau bagaimanapun, ini tidak selalunya mudah diakses oleh peminat atau penguji, dan ia tidak berfungsi di bawah spesifikasi voltan yang ditetapkan (biasanya di bawah 2.5 volt DC).

Tambahan pula, mungkin hanya terdapat tempat untuk satu bateri 1.5 volt dalam aplikasi berkuasa bateri. Nah, kemudian apa yang anda akan lakukan? Biasanya Gerbang logik IC boleh digantikan dengan get logik transistor. Untuk setiap get logik tertentu, hanya beberapa transistor secara amnya diperlukan, dan untuk logik penyongsang get NOT tipikal, hanya satu transistor diperlukan.

FET berbanding Transistor Bipolar

Transistor Kesan Medan (FET) lwn transistor bipolar : yang manakah pilihan yang lebih baik untuk litar logik voltan rendah? Satu ciri hebat FAKTA ialah rintangan 'pada' mereka adalah sangat rendah. Selain itu, mereka memerlukan arus get-turn-on yang sangat rendah.

Walau bagaimanapun, mereka mempunyai satu had dalam aplikasi voltan sangat rendah. Biasanya, had voltan pintu adalah satu volt atau lebih. Tambahan pula, voltan yang tersedia mungkin berkurangan di bawah julat kerja optimum FET jika perintang pengehad arus atau tarik-turun dipasang pada pintu pagar.

Sebaliknya, transistor pensuisan bipolar mempunyai kelebihan dalam voltan yang sangat rendah, aplikasi bateri tunggal kerana mereka hanya memerlukan 0.6 hingga 0.7 volt untuk menghidupkan.

Tambahan pula, kebanyakan FET biasa, yang biasanya dijual dalam pek gelembung di kedai elektronik terdekat anda selalunya lebih mahal daripada transistor bipolar. Juga, satu paket pukal transistor bipolar biasanya boleh dibeli dengan harga sepasang FET.

Pengendalian FET memerlukan penjagaan yang lebih ketara daripada pengendalian transistor bipolar. Penyalahgunaan eksperimen elektrostatik dan am menjadikan FET sangat terdedah kepada kerosakan. Komponen yang terbakar mungkin merosakkan malam eksperimen atau inovasi yang menyeronokkan dan kreatif, tidak lupa juga kesakitan emosi akibat nyahpepijat.

Asas Transistor Pensuisan

Contoh litar logik yang dijelaskan dalam artikel ini menggunakan transistor NPN bipolar kerana ia berpatutan dan tidak memerlukan pengendalian khas. Untuk mengelak daripada merosakkan peranti atau bahagian yang menyokongnya, langkah keselamatan yang sesuai hendaklah diambil sebelum menyambungkan litar anda.

Walaupun litar kami kebanyakannya berpusat pada Transistor Persimpangan Bipolar (BJT), ia boleh dibina dengan baik menggunakan teknologi FET.

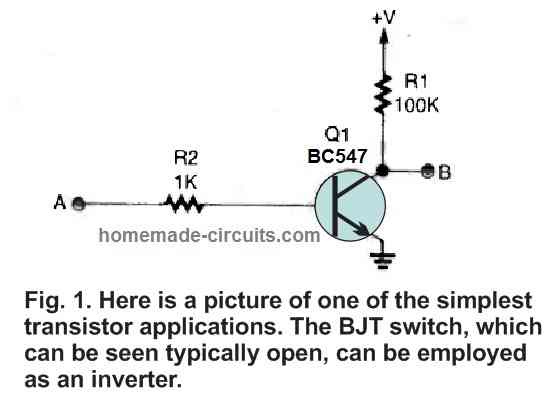

Litar suis asas ialah aplikasi transistor yang mudah, yang merupakan salah satu reka bentuk yang paling mudah.

Membuat NOT Gate dengan Transistor Tunggal

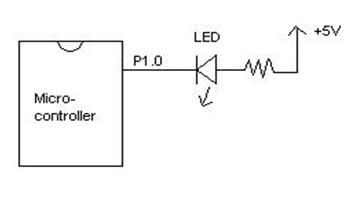

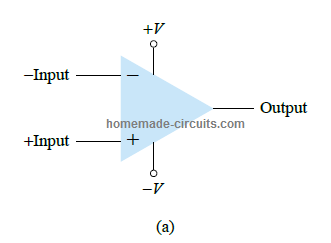

Skema suis transistor ditunjukkan dalam Rajah 1. Bergantung pada cara ia dilaksanakan dalam aplikasi tertentu, suis boleh dilihat sebagai sama ada disimpan rendah atau biasanya terbuka.

Gerbang logik penyongsang get NOT mudah boleh dicipta oleh litar pensuisan lurus yang ditunjukkan dalam Rajah 1 (di mana titik A ialah input). Gerbang NOT beroperasi sedemikian rupa sehingga jika tiada pincang DC disediakan pada tapak transistor (titik A; Q1), ia akan kekal ditutup, menghasilkan tinggi atau logik 1 (sama dengan aras V+) pada output ( titik B).

Walau bagaimanapun, transistor diaktifkan apabila pincang yang betul diberikan kepada asas Q1, menolak keluaran litar rendah atau kepada logik 0 (hampir sama dengan potensi sifar). Transistor, yang ditetapkan Q1, ialah transistor bipolar tujuan umum, atau BC547, yang biasanya digunakan dalam aplikasi pensuisan dan penguat kuasa rendah.

Mana-mana transistor yang setara dengannya (seperti 2N2222, 2N4401, dll.) akan berfungsi. Nilai R1 dan R2 telah dipilih untuk mencapai kompromi antara longkang arus rendah dan keserasian. Dalam semua reka bentuk, perintang adalah semua 1/4 watt, 5% unit.

Voltan bekalan boleh laras antara 1.4 dan 6 volt DC. Ambil perhatian bahawa litar boleh berfungsi seperti penampan apabila perintang beban dan sambungan output dialihkan ke pemancar transistor.

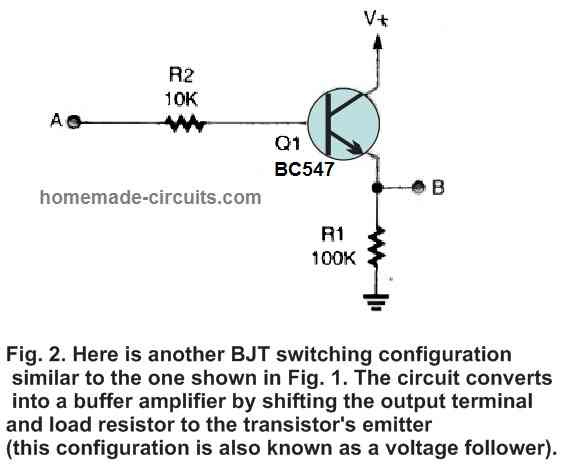

Membuat Pintu Penampan menggunakan BC547 BJT Tunggal

Pengikut voltan, atau penguat penimbal, ialah sejenis konfigurasi pensuisan logik yang sama dengan yang ditunjukkan dalam Rajah 2. Perlu diingatkan bahawa perintang beban dan terminal keluaran telah dialihkan daripada pengumpul transistor kepada pemancarnya dalam litar ini, iaitu perbezaan utama antara reka bentuk ini dan yang ditunjukkan dalam Rajah 1.

Fungsi transistor juga mungkin 'terbalik' dengan menggerakkan perintang beban dan terminal output ke hujung BJT yang lain.

Dalam erti kata lain, apabila tiada bias diberikan kepada input litar, output litar kekal rendah; bagaimanapun, apabila pincang voltan yang mencukupi dibekalkan kepada input litar, output litar bertukar tinggi. (Itu betul-betul bertentangan dengan apa yang berlaku dalam litar sebelumnya.)

Merekabentuk Gerbang Logik Dua Input menggunakan Transistor

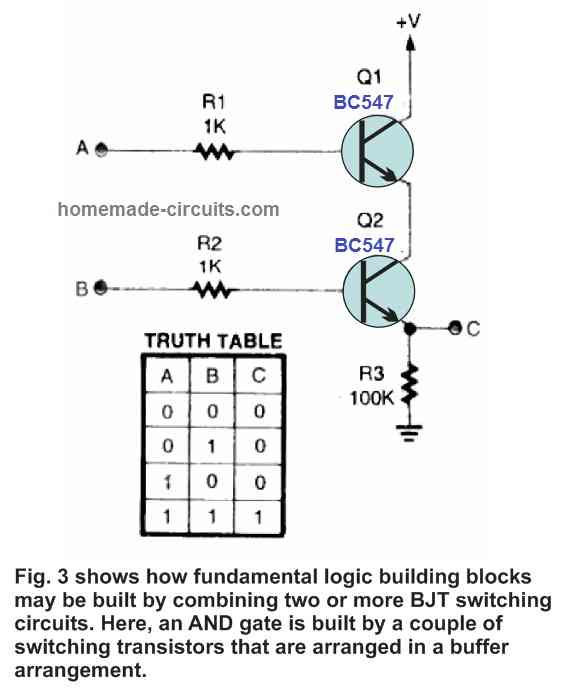

AND Gate menggunakan Dua Transistor

Rajah 3 menggambarkan cara get AND dua-input asas boleh dibuat menggunakan sepasang penimbal, bersama-sama dengan jadual kebenaran untuk get tersebut. Jadual kebenaran menggambarkan hasil keluaran bagi setiap set input yang berbeza. Titik A dan B digunakan sebagai input litar, dan titik C berfungsi sebagai output litar.

Adalah penting untuk diperhatikan daripada jadual kebenaran bahawa hanya satu set parameter input menghasilkan isyarat keluaran tinggi logik, manakala semua kombinasi input lain menghasilkan output rendah logik. Keluaran get AND dalam Rajah 3 kekal di bawah V+ apabila ia bertukar tinggi.

Ini berlaku kerana penurunan voltan antara dua transistor (Q1 dan Q2).

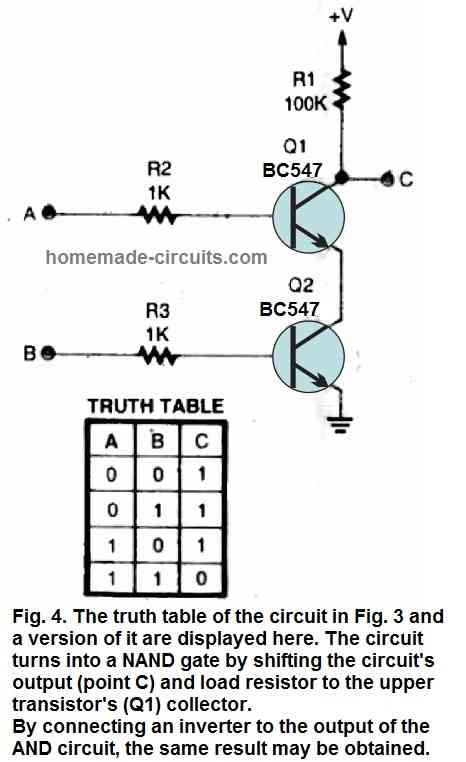

NAND Gate menggunakan Dua Transistor

Satu lagi varian litar dalam Rajah 3 dan jadual kebenaran yang berkaitan ditunjukkan dalam Rajah 4. Litar bertukar menjadi get NAND dengan mengalihkan keluaran (titik C) dan perintang keluaran kepada pengumpul transistor atas (Q1).

Oleh kerana kedua-dua Q1 dan Q2 perlu dihidupkan untuk menarik bahagian bawah R1 ke tanah, kehilangan voltan pada output C adalah tidak ketara.

Jika transistor AND atau gerbang NAND transistor memerlukan lebih daripada dua input, lebih banyak transistor boleh disambungkan dalam reka bentuk yang ditunjukkan untuk menyediakan tiga, empat, dsb., input AND atau get NAND.

Walau bagaimanapun, untuk mengimbangi kehilangan voltan transistor individu, V+ perlu dinaikkan secara sepadan.

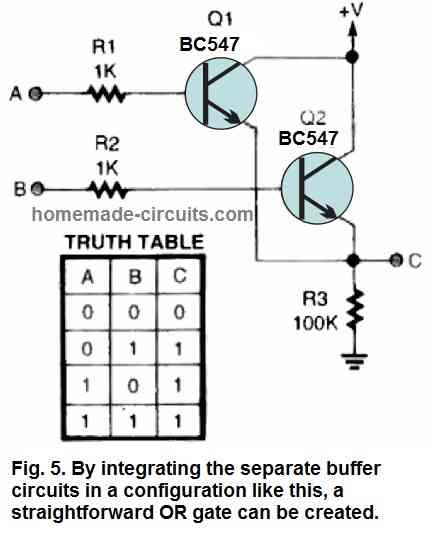

ATAU Gate menggunakan Dua Transistor

Satu lagi bentuk litar logik dengan dua input boleh dilihat dalam Rajah 5, bersama dengan jadual kebenaran litar OR-gate.

Keluaran litar adalah tinggi apabila sama ada input A atau input B ditolak tinggi, namun disebabkan oleh transistor lata, penurunan voltan melebihi 0.5 volt. Sekali lagi, angka yang dipaparkan menunjukkan bahawa terdapat voltan dan arus yang mencukupi untuk mengendalikan get transistor berikutnya.

Gerbang NOR menggunakan Dua Transistor

Rajah 6 menggambarkan get seterusnya pada senarai kami, get NOR dua input, bersama dengan jadual kebenarannya. Sama seperti bagaimana get AND dan NAND bertindak balas antara satu sama lain, litar OR dan NOR melakukan perkara yang sama.

Setiap gerbang yang dipaparkan mampu membekalkan pemacu yang mencukupi untuk mengaktifkan sekurang-kurangnya satu atau lebih gerbang transistor bersebelahan.

Aplikasi Gerbang Logik Transistor

Apakah yang anda lakukan dengan litar digital yang dijelaskan di atas yang anda miliki sekarang? Apa sahaja yang boleh anda capai dengan gerbang TTL atau CMOS konvensional, tetapi tanpa perlu risau tentang sekatan voltan bekalan. Berikut ialah beberapa aplikasi get transistor-logik dalam tindakan.

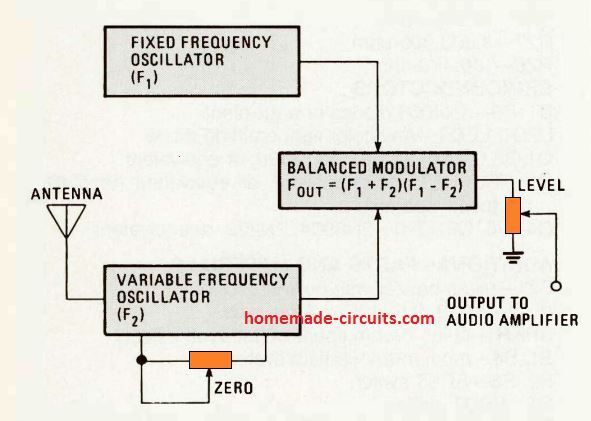

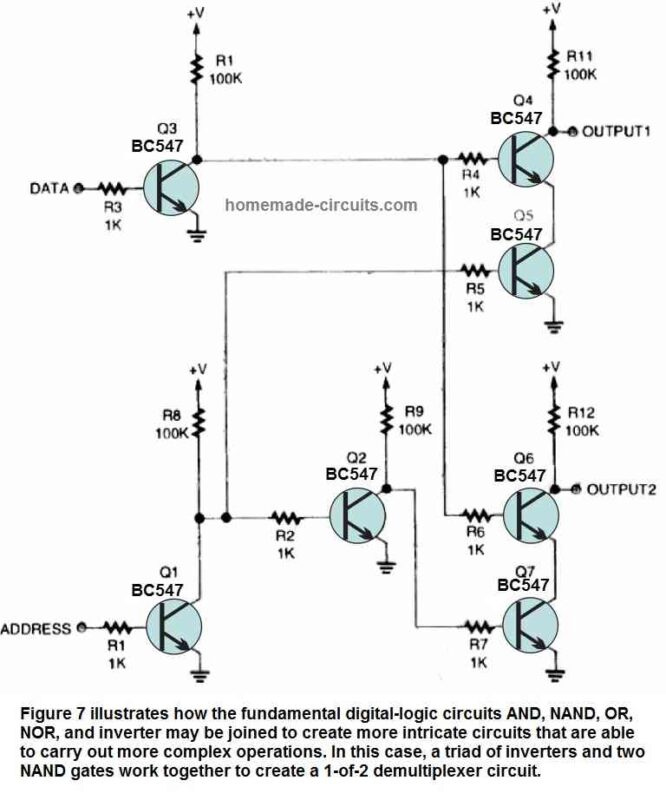

Litar Demultiplexer

Demultiplexer 1-of-2 dengan tiga get NOT dan dua litar NAND dilihat dalam Rajah 7. Output yang sesuai dipilih menggunakan 'input alamat' satu-bit, yang mungkin sama ada OUTPUT1 atau OUTPUT2, sementara maklumat pemanduan digunakan ke litar menggunakan input DATA.

Litar ini beroperasi paling berkesan apabila kadar data dikekalkan di bawah 10 kHz. Fungsi litar adalah mudah. Input DATA dibekalkan dengan isyarat yang diperlukan, yang menghidupkan Q3 HIDUP dan menyongsangkan data masuk pada pengumpul Q3.

Output Q1 dipacu tinggi jika input ADDRESS rendah (dibumikan atau tiada isyarat disediakan). Pada pengumpul Q1, keluaran tinggi dibahagikan kepada dua laluan. Dalam laluan pertama, output Q1 dibekalkan ke pangkalan Q5 (salah satu daripada dua kaki get NAND input), menghidupkannya dan oleh itu 'mengaktifkan' get NAND yang terdiri daripada Q4 dan Q5.

Dalam laluan kedua, keluaran tinggi Q1 dibekalkan secara serentak ke dalam input get NOT lain (Q2). Selepas menjalani penyongsangan berganda, keluaran Q2 menjadi rendah. Rendah ini dibekalkan pangkalan Q7 (satu terminal pintu NAND kedua, terdiri daripada Q6 dan Q7), dengan itu mematikan litar NAND.

Sebarang maklumat atau isyarat yang digunakan pada input DATA tiba di OUTPUT1 dalam keadaan ini. Sebagai alternatif, keadaan diterbalikkan jika isyarat tinggi diberikan kepada input ADDRESS. Bermakna, sebarang maklumat yang diberikan kepada litar akan ditunjukkan di OUTPUT2 memandangkan get Q4/Q5 NAND dinyahdayakan dan get Q6/Q7 NAND didayakan.

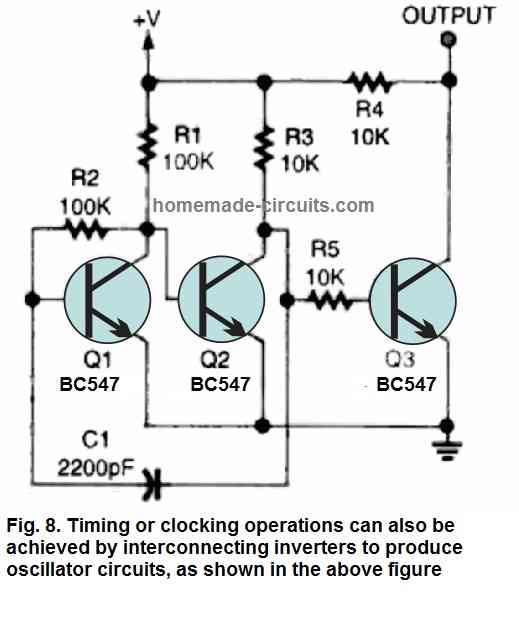

Litar Pengayun (Penjana Jam)

Aplikasi get logik transistor kami yang seterusnya, yang digambarkan dalam Rajah 8, ialah penjana jam asas (juga dikenali sebagai pengayun) yang diperbuat daripada tiga penyongsang get NOT biasa (satu daripadanya dipincang menggunakan perintang maklum balas, R2, yang memasukkannya ke dalam kawasan analog).

Untuk menyelaraskan keluaran, get NOT ketiga (Q3) yang menyampaikan pelengkap kepada keluaran pengayun disertakan. Nilai C1 boleh ditambah atau dikurangkan untuk menukar kekerapan operasi litar. Bentuk gelombang keluaran mempunyai frekuensi sekitar 7 kHz dengan V+ pada 1.5 volt DC, menggunakan nilai komponen yang ditunjukkan.

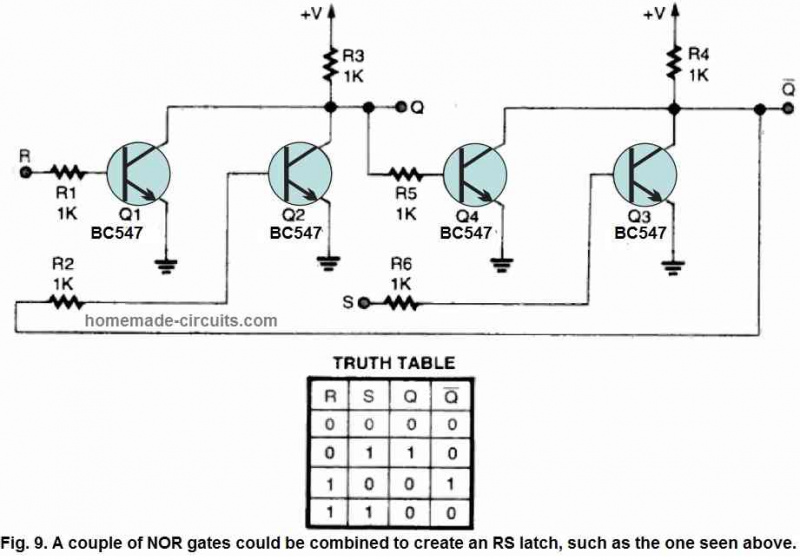

Litar Selak RS

Rajah 9 menunjukkan litar aplikasi terakhir kami, selak RS yang terdiri daripada dua get NOR. Untuk memastikan pemacu keluaran yang sihat pada output Q dan Q, perintang R3 dan R4 dilaraskan kepada 1k ohm.

Jadual kebenaran selak RS dipaparkan bersama reka bentuk skematik. Ini hanyalah beberapa ilustrasi bagi beberapa litar get logik yang boleh dipercayai, voltan rendah, digital, yang boleh dibuat menggunakan transistor individu.

Litar Menggunakan Logik Transistor Memerlukan Terlalu Banyak Bahagian

Banyak isu boleh diselesaikan menggunakan semua litar logik transistor voltan rendah ini. Walau bagaimanapun, menggunakan terlalu banyak gerbang transistor ini boleh membawa kepada isu baharu.

Bilangan transistorizes dan perintang mungkin menjadi agak besar jika aplikasi yang anda bina mengandungi sejumlah besar gerbang, menduduki ruang yang berharga.

Menggunakan tatasusunan transistor (banyak transistor yang disertakan dalam plastik) dan perintang SIP (Single Inline Package) sebagai ganti unit individu adalah satu cara untuk menyelesaikan masalah ini.

Pendekatan di atas boleh menjimatkan satu tan ruang pada pcb sambil mengekalkan prestasi yang sama dengan yang setara dengan saiz penuh mereka. Tatasusunan transistor ditawarkan dalam pembungkusan pelekap permukaan, lubang telus 14-pin dan pek empat.

Bagi kebanyakan litar, mencampurkan jenis transistor mungkin agak boleh diterima.

Walau bagaimanapun, adalah dinasihatkan bahawa penguji berfungsi dengan satu jenis transistor untuk membina litar logik transistor (bermaksud jika anda mencipta bahagian get menggunakan BC547, kemudian cuba gunakan BJT yang sama untuk membuat get yang lain juga).

Alasannya ialah pelbagai varian transistor mungkin mempunyai sifat yang agak berbeza dan dengan itu mungkin berkelakuan berbeza.

Sebagai contoh, bagi sesetengah transistor, had suis-ON asas mungkin lebih besar atau lebih kecil daripada yang lain, atau satu boleh mempunyai keuntungan semasa keseluruhan yang sedikit lebih tinggi atau lebih rendah.

Sebaliknya, kos membeli kotak pukal bagi satu jenis transistor juga mungkin lebih rendah. Prestasi litar anda akan dipertingkatkan jika get logik anda dibina menggunakan transistor yang sepadan, dan projek keseluruhannya akan menjadi lebih bermanfaat akhirnya.