The transistor kesan medan (FET) adalah peranti elektronik di mana medan elektrik digunakan untuk mengatur aliran arus. Untuk melaksanakannya, kemungkinan perbezaan diterapkan di terminal gerbang dan terminal sumber, yang mengubah kekonduksian antara terminal longkang dan sumber menyebabkan arus terkawal mengalir melintasi terminal ini.

FET dipanggil transistor unipolar kerana ini dirancang untuk beroperasi sebagai peranti jenis pembawa tunggal. Anda akan menemui pelbagai jenis transistor kesan medan.

Simbol

Simbol grafik untuk JFET saluran-n dan saluran-p dapat dilihat dalam gambar-gambar berikut.

Anda dapat dengan jelas memperhatikan bahawa tanda panah yang menghala ke dalam untuk peranti saluran-n menunjukkan arah di mana sayaG(arus gerbang) seharusnya mengalir ketika persimpangan p-n dipihak ke hadapan.

Sekiranya peranti saluran-p kondisinya sama kecuali perbezaan arah simbol anak panah.

Perbezaan antara FET dan BJT

Transistor kesan medan (FET) adalah peranti tiga terminal yang direka untuk pelbagai aplikasi litar yang melengkapkan, hingga tahap yang besar, dengan transistor BJT.

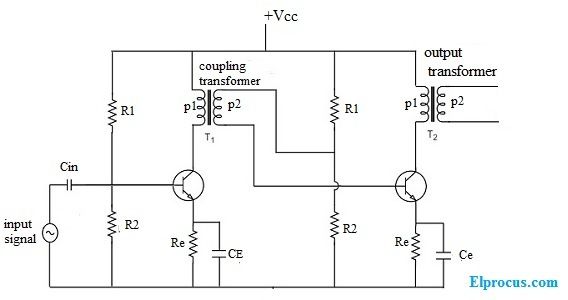

Walaupun anda akan menemui perbezaan yang signifikan antara BJT dan JFET, sebenarnya terdapat beberapa ciri yang sesuai yang akan dibincangkan dalam perbincangan berikut. Perbezaan utama antara perangkat ini adalah BJT adalah perangkat yang dikendalikan arus seperti yang ditunjukkan pada Gambar 5.1a, sementara transistor JFET adalah perangkat yang dikendalikan voltan seperti yang ditunjukkan pada Gambar 5.1b.

Ringkasnya, I semasaCdalam Rajah 5.1a adalah fungsi langsung dari tahap IB. Untuk FET arus I adalah fungsi voltan VGSdiberikan kepada litar input seperti yang ditunjukkan dalam Rajah 5.1b.

Dalam kedua-dua keadaan arus rangkaian output akan diatur oleh parameter rangkaian input. Dalam satu keadaan tahap semasa dan yang lain voltan terpakai.

Sama seperti npn dan pnp untuk transistor bipolar, anda akan menemui transistor kesan medan n-saluran dan p-saluran. Tetapi, anda harus ingat bahawa transistor BJT adalah peranti bipolar awalan bi - menunjukkan bahawa tahap konduksi adalah fungsi dua pembawa cas, elektron dan lubang.

FET sebaliknya adalah a peranti unipolar yang bergantung sepenuhnya pada pengaliran elektron (saluran n) atau lubang (saluran-p).

Ungkapan 'medan-kesan' dapat dijelaskan seperti ini: kita semua menyedari kekuatan magnet kekal untuk menarik filing logam ke arah magnet tanpa hubungan fizikal. Dengan cara yang serupa di dalam FET, medan elektrik dihasilkan oleh caj yang ada yang mempengaruhi jalan konduksi litar output tanpa mempunyai hubungan langsung antara kuantiti yang dikawal dan dikawal. Mungkin salah satu ciri FET yang paling penting adalah impedans inputnya yang tinggi.

Mulai dari magnitud 1 hingga ratus megohms, ia secara signifikan melebihi julat rintangan input normal dari konfigurasi BJT, atribut yang sangat penting semasa mengembangkan model penguat ac linear.

Walau bagaimanapun, BJT mempunyai kepekaan yang lebih besar terhadap variasi isyarat input. Maknanya, perubahan arus keluaran biasanya lebih ketara bagi BJT daripada FET untuk jumlah perubahan voltan input yang sama.

Oleh kerana itu, kenaikan voltan ac standard untuk penguat BJT boleh menjadi jauh lebih tinggi berbanding dengan FET.

Secara umum, FET jauh lebih tahan ketahanan daripada BJT, dan juga strukturnya bersaiz lebih kecil berbanding BJT, yang menjadikannya sangat sesuai untuk disisipkan sebagai litar bersepadu (IC)kerepek.

Ciri-ciri struktur beberapa FET, sebaliknya, boleh memungkinkan mereka menjadi lebih sensitif terhadap hubungan fizikal daripada BJT.

Lebih Banyak Hubungan BJT / JFET

- Untuk BJT VMENJADI= 0.7 V adalah faktor penting untuk memulakan analisis konfigurasinya.

- Begitu juga dengan parameter IG= 0 A biasanya merupakan perkara pertama yang dipertimbangkan untuk analisis litar JFET.

- Untuk konfigurasi BJT, IBsering menjadi faktor pertama yang perlu ditentukan.

- Begitu juga, untuk JFET, biasanya adalah VGS.

Dalam artikel ini kita akan memfokuskan pada JFET atau transistor kesan medan persimpangan, dalam artikel seterusnya kita akan membahas tentang transistor effcet medan-oksida-semikonduktor atau MOS-FET.

PEMBINAAN DAN KARAKTERISTIK JFET

Semasa kami belajar earlet, JFET mempunyai 3 petunjuk. Salah satunya mengawal aliran arus antara dua yang lain.

Sama seperti BJT, di JFET juga peranti saluran-n digunakan lebih menonjol daripada rakan-rakan saluran-p, kerana peranti n cenderung lebih cekap dan mesra pengguna dibandingkan dengan peranti p.

Dalam rajah berikut kita dapat melihat struktur asas atau pembinaan JFET saluran n. Kita dapat melihat bahawa komposisi jenis-n membentuk saluran utama melintasi lapisan jenis-p.

Bahagian atas saluran jenis-n digabungkan melalui hubungan Ohmik dengan istilah bernama saluran (D), sementara bahagian bawah saluran yang sama juga dihubungkan melalui hubungan Ohmik dengan terminal lain bernama sumber (S).

Beberapa bahan jenis p dihubungkan bersama dengan terminal yang disebut sebagai pintu gerbang (G). Pada dasarnya kita dapati bahawa terminal longkang dan sumber bergabung dengan hujung saluran jenis-n. Terminal gerbang bergabung dengan sepasang bahan saluran-p.

Apabila tidak ada voltan yang dikenakan pada jfet, dua persimpangan p-nnya tanpa syarat berat sebelah. Dalam situasi ini terdapat wilayah penipisan pada setiap persimpangan seperti yang ditunjukkan pada gambar di atas, yang terlihat seperti wilayah p-n dioda tanpa bias.

Analogi Air

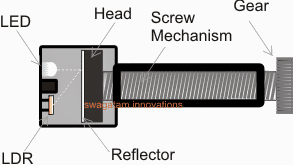

Operasi kerja dan kawalan JFET dapat difahami melalui analogi air berikut.

Di sini, tekanan air dapat dibandingkan dengan magnitud voltan yang berlaku dari longkang ke arah sumber.

Aliran air dapat dibandingkan dengan aliran elektron. Mulut keran meniru terminal sumber JFET, sementara bahagian atas keran di mana air dipaksa menggambarkan Saliran JFET.

Tombol ketuk bertindak seperti Gerbang JFET. Dengan bantuan potensi input, ia mengawal aliran elektron (pengisian) dari longkang ke sumber, sama seperti tombol paip mengawal aliran air pada bukaan mulut.

Dari struktur JFET kita dapat melihat bahawa terminal longkang dan sumber berada di hujung saluran-n, dan kerana istilah ini berdasarkan aliran elektron kita dapat menulis:

VGS= 0 V, VDSBeberapa Nilai Positif

Dalam Rajah 5.4 kita dapat melihat voltan positif VDSdigunakan di seluruh saluran-n. Terminal pintu masuk terus ke sumber untuk mewujudkan keadaan VGS= 0V. Ini membolehkan pintu gerbang dan terminal sumber berada pada potensi yang sama, dan menghasilkan kawasan penipisan hujung bawah setiap bahan p, persis seperti yang kita lihat pada rajah pertama di atas dengan keadaan tanpa bias.

Sebaik sahaja voltan VDD(= VDS) diaplikasikan, elektron ditarik ke arah terminal pengaliran, menghasilkan aliran ID arus konvensional, seperti yang ditunjukkan pada Gambar 5.4.

Arah aliran muatan menunjukkan bahawa arus longkang dan sumber sama besarnya (ID= SayaS). Sesuai dengan keadaan yang digambarkan dalam Gambar 5.4, aliran muatan tampak tidak terbatas, dan hanya dipengaruhi oleh rintangan saluran n antara saluran dan sumbernya.

Anda mungkin melihat bahawa kawasan penipisan lebih besar di bahagian atas kedua-dua jenis bahan p. Perbezaan ukuran wilayah ini dijelaskan secara ideal melalui Gambar 5.5. Mari kita bayangkan mempunyai rintangan yang seragam di saluran-n, ini boleh dibahagi kepada bahagian-bahagian yang ditunjukkan dalam Rajah 5.5.

I semasaDboleh membina julat voltan melalui saluran seperti yang ditunjukkan dalam rajah yang sama. Akibatnya, bahagian atas bahan jenis-p akan terbalik terbalik dengan tingkat sekitar 1.5 V, dengan wilayah bawah hanya dibalikkan oleh 0.5 V.

Titik bahawa persimpangan p-n adalah bias terbalik sepanjang keseluruhan saluran menimbulkan arus gerbang dengan ampere sifar seperti yang ditunjukkan dalam rajah yang sama. Ciri ini yang membawa kepada IG= 0 A adalah ciri penting JFET.

Sebagai VDSpotensi ditingkatkan dari 0 menjadi beberapa volt, arus meningkat mengikut undang-undang Ohm dan plot IDbaris 5DSboleh kelihatan seperti yang terbukti dalam Rajah 5.6.

Ketepatan perbandingan plot menunjukkan bahawa untuk kawasan nilai rendah VDS, rintangan pada dasarnya seragam. Sebagai VDSnaik dan mendekati tahap yang dikenal sebagai VP pada Gambar 5.6, kawasan penipisan melebar seperti yang ditunjukkan pada Gambar 5.4.

Ini menghasilkan penurunan lebar saluran yang jelas. Jalur konduksi yang menurun membawa kepada peningkatan rintangan yang menimbulkan lengkung Gambar 5.6.

Semakin mendatar lengkung, semakin tinggi rintangan, menunjukkan bahawa rintangan semakin hampir ke ohm 'tak terhingga' di kawasan mendatar. Apabila VDSmeningkat hingga terlihat di mana dua wilayah penipisan mungkin 'bersentuhan' seperti yang ditunjukkan pada Gambar 5.7, menimbulkan situasi yang dikenal sebagai pinch-off.

Jumlah di mana VDSmengembangkan keadaan ini dipanggil mencubit voltan dan ia dilambangkan oleh VPseperti yang ditunjukkan dalam Rajah 5.6. Secara amnya, kata pinch-off menyesatkan kerana menyiratkan I semasaD'dicubit' dan jatuh ke 0 A. Seperti yang terbukti dalam Rajah 5.6, ini hampir tidak kelihatan dalam kes ini. SayaDmengekalkan tahap tepu yang dicirikan sebagai IDSSdalam Rajah 5.6.

Kebenarannya adalah saluran yang sangat kecil terus ada, dengan arus kepekatan yang sangat tinggi.

Titik bahawa ID tidak jatuh pada mencubit dan mempertahankan tahap tepu seperti yang ditunjukkan pada Gambar 5.6 disahkan dengan bukti berikut:

Oleh kerana tidak ada arus pengaliran menghilangkan kemungkinan tahap potensi yang beragam melalui bahan saluran-n untuk menentukan jumlah perubahan bias terbalik di sepanjang persimpangan p-n. Hasil akhirnya adalah kehilangan taburan kawasan penipisan yang dicetuskan mencubit bermula dengan.

Semasa kita meningkatkan VDSdi atas VP, kawasan hubungan rapat di mana kedua-dua kawasan penipisan akan saling berhadapan dengan peningkatan panjang sepanjang saluran. Walau bagaimanapun, tahap ID pada dasarnya tidak berubah.

Demikianlah saat VDSlebih tinggi daripada Vhlm, JFET memperoleh ciri sumber semasa.

Seperti yang terbukti dalam Rajah 5.8 arus dalam JFET ditentukan pada ID= SayaDSS, tetapi voltan VDSlebih tinggi daripada VP ditentukan oleh beban yang disambungkan.

Pemilihan notasi IDSS didasarkan pada kenyataan bahawa arus Arus ke Sumber mempunyai pautan litar pintas melintasi pintu ke sumber.

Penyelidikan lebih lanjut memberi kami penilaian berikut:

SayaDSSadalah arus pengaliran tertinggi untuk JFET dan ditentukan oleh syarat VGS= 0 V dan VDS> | VP |.

Perhatikan bahawa dalam Rajah 5.6 VGSialah 0V untuk keseluruhan lengkungan. Pada bahagian berikut kita akan belajar bagaimana atribut Fig 5.6 dipengaruhi sebagai tahap VGSbervariasi.

VGS <0V

Volatasi yang berlaku di seberang pintu dan sumber ditandakan sebagai VGS, yang bertanggung jawab untuk mengendalikan operasi JFET.

Sekiranya kita mengambil contoh BJT, sama seperti lengkung ICvs VINIditentukan untuk pelbagai tahap IB, juga keluk IDvs VDSuntuk pelbagai tahap VGSboleh dibuat untuk rakan sejawat JFET.

Untuk ini terminal gerbang ditetapkan pada potensi rendah yang berlanjutan di bawah tahap potensi sumber.

Merujuk pada Gambar.5.9 di bawah, a -1V diterapkan di terminal gerbang / sumber untuk V berkurangDStahap.

Objektif bias potensi negatif VGSadalah mengembangkan kawasan penipisan yang menyerupai keadaan VGS= 0, tetapi pada V berkurang dengan ketaraDS.

Ini menyebabkan pintu masuk mencapai titik tepu dengan tahap V yang lebih rendahDSseperti yang ditunjukkan pada Gambar 5.10 (VGS= -1V).

Tahap saturatio yang sesuai untuk IDboleh didapati berkurang dan sebenarnya semakin berkurang sebagai VGSdibuat lebih negatif.

Anda dapat melihat dengan jelas dalam Rajah 5.10 bagaimana voltan pinch-off terus menurun dengan bentuk parabola sebagai VGSsemakin negatif.

Akhirnya, apabila VGS= -Vhlm, ia menjadi cukup negatif untuk menetapkan tahap tepu yang akhirnya 0 mA. Pada tahap ini, JFET benar-benar 'dimatikan'.

Tahap VGSyang menyebabkan sayaDuntuk mencapai 0 mA dicirikan oleh VGS= VP, di mana VPadalah voltan negatif untuk peranti saluran n dan voltan positif untuk JFET saluran p.

Biasanya, anda mungkin mendapati kebanyakan lembaran data JFET menunjukkan mencubit voltan dinyatakan sebagai VGS (mati)bukannya VP.

Kawasan di sebelah kanan lokus pinch-off pada gambar di atas adalah tempat yang biasa digunakan dalam penguat linear untuk mencapai isyarat bebas distorsi. Kawasan ini umumnya disebut arus pemalar berterusan, ketepuan atau linear.

Perintang yang dikawal voltan

Kawasan yang berada di sebelah kiri lokus pinch-off dalam rajah yang sama, disebut wilayah ohmik atau kawasan rintangan terkawal voltan.

Di rantau ini, alat ini sebenarnya dapat dikendalikan sebagai resistor berubah-ubah (misalnya dalam aplikasi kawalan keuntungan automatik), dengan rintangannya dikendalikan melalui potensi pintu / sumber yang diterapkan.

Anda dapat melihat bahawa cerun setiap lengkung yang juga menandakan rintangan longkang / sumber JFET untuk VDS

Ketika kita menjadikan VGS lebih tinggi dengan potensi negatif, kemiringan setiap lekukan semakin mendatar, menunjukkan peningkatan tahap rintangan secara proporsional.

Kami dapat memperoleh perkiraan awal yang baik ke tahap rintangan berkenaan dengan voltan VGS, melalui persamaan berikut.

p-Channel JFET Berfungsi

Susun atur dan pembinaan JFET saluran p sama persis dengan rakan saluran-n, kecuali bahawa kawasan bahan jenis p dan n dibalikkan, seperti yang ditunjukkan di bawah:

Arah aliran arus juga dapat dilihat sebagai terbalik, bersama dengan polariti voltan sebenar VGS dan VDS. Sekiranya JFET saluran p, saluran akan terkekang sebagai tindak balas terhadap peningkatan potensi positif di seluruh pintu / sumber.

Notasi dengan langganan berganda untuk VDSakan menimbulkan voltan negatif untuk VDS, seperti yang ditunjukkan pada ciri-ciri Rajah 5.12. Di sini, anda boleh menemui sayaDSSpada 6 mA, sementara voltan pinch-off pada VGS= + 6V.

Jangan bingung kerana kehadiran tanda tolak untuk VDS. Ini hanya menunjukkan bahawa sumber mempunyai potensi yang lebih tinggi daripada saluran pembuangan.

Anda dapat melihat bahawa lengkung untuk V tinggiDStahap tiba-tiba naik ke nilai yang kelihatan tidak terhad. Kenaikan yang ditunjukkan yang menegak melambangkan keadaan kerosakan, yang bermaksud arus melalui peranti saluran dikawal sepenuhnya oleh litar luaran pada masa ini.

Walaupun ini tidak dapat dilihat pada Rajah 5.10 untuk peranti saluran n, kemungkinan terdapat voltan yang cukup tinggi.

Wilayah ini dapat dihapuskan sekiranya VDS (maksimum)dicatat dari lembar data peranti, dan peranti dikonfigurasi sedemikian rupa sehingga V yang sebenarnyaDSnilai lebih rendah daripada nilai yang dinyatakan ini untuk sebarang VGS.

Sebelumnya: 5 Litar Penguat 40 Watt Terbaik Terokai Seterusnya: Lembaran Data 2N3055, Pinout, Litar Aplikasi