JTAG (Joint Test Action Group) ialah piawaian IEEE 1149.1 yang mantap yang dibangunkan pada tahun 1980 untuk menyelesaikan isu pembuatan yang berlaku dalam papan elektronik atau papan litar bercetak . Teknologi ini digunakan untuk menyediakan akses ujian yang mencukupi untuk setiap papan kompleks apabila akses ujian semakin berkurangan. Oleh itu, teknologi imbasan sempadan dilancarkan & piawaian JTAG atau spesifikasi JTAG ditubuhkan. Kerumitan elektronik telah meningkat dari hari ke hari, jadi spesifikasi JTAG telah menjadi format ujian yang diterima untuk menguji unit elektronik yang rumit & padat. Artikel ini membincangkan gambaran keseluruhan a JTAG protokol – bekerja dengan aplikasi.

Apakah JTAG?

Nama yang diberikan kepada Port Akses Ujian Standard IEEE 1149.1 serta Seni Bina Sempadan-Imbasan dikenali sebagai JTAG (Kumpulan Tindakan Ujian Bersama). Seni bina imbasan sempadan ini kebanyakannya digunakan dalam komputer pemproses kerana pemproses pertama dengan JTAG dikeluarkan oleh Intel. Piawaian IEEE ini hanya mentakrifkan cara litar komputer diuji untuk mengesahkan sama ada ia berfungsi dengan betul selepas prosedur pembuatan. Pada papan litar, ujian dilakukan untuk memeriksa sambungan pateri.

Kumpulan Tindakan Ujian Bersama menyediakan paparan pin keluar untuk penguji dengan setiap pad IC yang membantu dalam mengenal pasti sebarang kerosakan dalam papan litar. Sebaik sahaja protokol ini disambungkan kepada cip, ini boleh memasang probe pada cip dengan membenarkan pembangun mengawal cip serta sambungannya dengan cip lain. Antara muka dengan kumpulan Tindakan Ujian Bersama juga boleh digunakan oleh Pembangun untuk menyalin perisian tegar ke memori tidak meruap dalam peranti elektronik.

Konfigurasi/Semat Keluar

Kumpulan Tindakan Ujian Bersama termasuk 20-pin di mana setiap pin dan fungsinya dibincangkan di bawah.

Pin1 (VTref): Ini ialah pin voltan rujukan sasaran yang digunakan untuk menyambung kepada bekalan kuasa utama sasaran yang berjulat dari 1.5 hingga 5.0VDC.

Pin2 (Vsupply): Ini ialah voltan bekalan sasaran yang digunakan untuk menyambung bekalan voltan utama sasaran 1.5VDC – 5.0VDC.

Pin3 (nTRST): Ini ialah pin tetapan semula ujian yang digunakan untuk menetapkan semula mesin keadaan pengawal TAP.

Pin (4, 6, 8, 10, 12, 14, 16, 18 & 20): Ini adalah pin GND biasa.

Pin5 (TDI): Ini adalah Data Ujian Dalam pin. Data ini dialihkan ke peranti sasaran. Pin ini mesti ditarik ke atas pada keadaan yang ditetapkan pada papan sasaran.

Pin7 (TMS): Ini ialah pin Keadaan Mod Ujian yang ditarik untuk menentukan keadaan seterusnya mesin keadaan pengawal TAP.

Pin9 (TCK): Ini ialah pin jam ujian yang menyegerakkan operasi mesin keadaan dalaman dalam pengawal TAP.

Pin11 (RTCK): Ini ialah pin TCK Pulangan Input yang digunakan dalam peranti yang menyokong masa penyesuaian.

Pin13 (TDO): Ini ialah pin Test Data Out, jadi data dialihkan keluar dari peranti sasaran ke dalam Flyswatter.

Pin15 (nSRST): Ini ialah pin Set Semula Sistem Sasaran yang disambungkan kepada isyarat set semula utama sasaran.

Pin 17 & 19 (NC): Ini bukan pin bersambung.

JTAG Bekerja

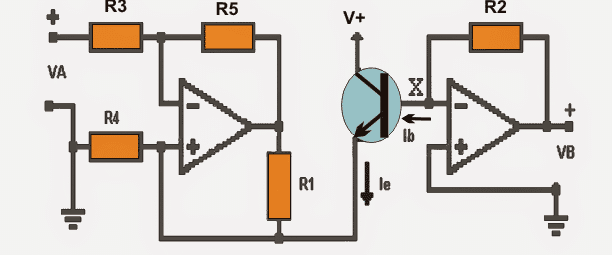

Penggunaan asal JTAG adalah untuk ujian sempadan. Di sini, adalah papan litar bercetak mudah termasuk dua IC seperti CPU & FPGA . Papan biasa mungkin termasuk banyak IC. Secara umum, IC termasuk banyak pin yang disambungkan bersama dengan banyak sambungan. Di sini, dalam rajah berikut, hanya empat sambungan ditunjukkan.

Jadi jika anda mereka bentuk banyak papan di mana setiap papan mempunyai beribu-ribu sambungan. Dalam itu, terdapat beberapa papan yang buruk. Jadi kita perlu menyemak papan mana yang berfungsi dan mana yang tidak berfungsi. Untuk itu, Kumpulan Tindakan Ujian Bersama telah direka bentuk.

Protokol ini boleh menggunakan pin kawalan semua cip tetapi dalam rajah berikut, Kumpulan Tindakan Ujian Bersama akan membuat semua pin output CPU & semua pin input FPGA. Selepas itu, dengan menghantar sejumlah data daripada pin CPU & membaca nilai pin daripada FPGA, JTAG menyatakan bahawa sambungan papan PCB adalah baik.

Sebenarnya, Kumpulan Tindakan Ujian Bersama merangkumi empat isyarat logik TDI, TDO, TMS & TCK. Dan isyarat ini perlu disambungkan dengan cara tertentu. Pada mulanya, TMS & TCK disambungkan selari dengan semua IC JTAG.

Selepas itu, kedua-dua TDI & TDO disambungkan untuk membentuk rantai. Seperti yang anda boleh perhatikan, setiap IC yang mematuhi JTAG termasuk 4-pin yang digunakan untuk JTAG di mana 3-pin adalah input dan pin ke-4 adalah output. Pin kelima seperti TRST adalah pilihan. Biasanya, pin JTAG tidak dikongsi untuk tujuan lain.

Dengan menggunakan Kumpulan Tindakan Ujian Bersama, semua IC menggunakan ujian sempadan yang sebab asalnya dicipta oleh JTAG. Pada masa ini, penggunaan protokol ini telah diperluaskan untuk membenarkan perkara yang berbeza seperti mengkonfigurasi FPGA & selepas itu JTAG digunakan dalam teras FPGA untuk tujuan penyahpepijatan.

Seni Bina JTAG

Seni bina JTAG ditunjukkan di bawah. Dalam seni bina ini, semua isyarat di antara logik teras peranti & pin terganggu melalui laluan imbasan bersiri yang dipanggil BSR atau Daftar Imbasan Sempadan. BSR ini merangkumi pelbagai ‘sel’ imbasan sempadan. Secara amnya, sel imbasan sempadan ini tidak kelihatan tetapi ia boleh digunakan untuk menetapkan atau membaca nilai dalam mod ujian daripada pin peranti.

Antara muka JTAG yang dipanggil TAP atau Test Access Port menggunakan isyarat berbeza untuk menyokong operasi imbasan sempadan seperti TCK, TMS, TDI, TDO dan TRST.

- Isyarat TCK atau Jam Ujian hanya menyegerakkan operasi dalam mesin keadaan.

- Isyarat TMS atau Mod Ujian Pilih sampel pada kelebihan isyarat jam ujian untuk menentukan keadaan seterusnya.

- Isyarat TDI atau Data Ujian Dalam menandakan data yang dialihkan ke dalam peranti ujian sebaliknya logik pengaturcaraan. Apabila mesin keadaan dalam berada dalam keadaan yang betul maka ia diambil sampel pada kelebihan TCK yang semakin meningkat.

- Isyarat TDO atau Test Data Out menandakan data yang dialih keluar peranti ujian sebaliknya logik pengaturcaraan. Apabila mesin keadaan dalam berada dalam keadaan yang betul maka ia sah pada tepi menurun TCK

- TRST atau Test Reset ialah pin pilihan yang digunakan untuk menetapkan semula mesin keadaan pengawal TAP.

Pengawal TAP

Titik akses ujian dalam seni bina JTAG terdiri daripada pengawal TAP, daftar arahan & daftar data ujian. Pengawal ini termasuk mesin keadaan ujian yang bertanggungjawab untuk membaca isyarat TMS & TCK. Di sini, pin i/p data hanya digunakan untuk memuatkan data ke dalam sel sempadan di antara teras IC & pin fizikal, dan juga memuatkan data ke dalam salah satu daftar data atau ke dalam daftar arahan. Pin data o/p digunakan untuk membaca data sama ada daripada daftar atau sel sempadan.

Mesin keadaan pengawal TAP dikawal oleh TMS dan ia dikawal oleh TCK. Mesin keadaan menggunakan dua laluan untuk menandakan dua mod berbeza seperti mod arahan & mod data.

Mendaftar

Terdapat dua jenis daftar yang tersedia dalam imbasan sempadan. Setiap peranti yang mematuhi termasuk min dua atau lebih daftar data & satu daftar arahan.

Daftar Arahan

Daftar arahan digunakan untuk menyimpan arahan semasa. Jadi datanya digunakan oleh pengawal TAP untuk memutuskan perkara yang hendak dilaksanakan dengan isyarat yang diperolehi. Selalunya, data daftar arahan akan menerangkan kepada mana satu isyarat daftar data mesti dihantar.

Daftar Data

Daftar data boleh didapati dalam tiga jenis BSR (Daftar Imbasan Sempadan), BYPASS & daftar KOD ID. Dan juga, daftar data lain mungkin ada, namun ia tidak diperlukan sebagai elemen piawaian JTAG.

Daftar Imbasan Sempadan (BSR)

BSR ialah daftar data ujian utama yang digunakan untuk mengalih data dari dan ke pin I/O peranti.

BYPASS

Bypass ialah daftar bit tunggal yang digunakan untuk menghantar data daripada TDI – TDO. Jadi ia membolehkan peranti tambahan dalam litar diuji dengan overhed minimum.

KOD ID

Daftar data jenis ini termasuk kod ID serta nombor semakan untuk peranti. Jadi data ini membolehkan peranti disambungkan ke fail BSDL (Bahasa Penerangan Imbasan Sempadan). Fail ini termasuk butiran konfigurasi Imbasan Sempadan untuk peranti.

Kerja JTAG adalah, pada mulanya, mod arahan dipilih di mana salah satu keadaan dalam 'laluan' mod ini membolehkan operator jam dalam arahan oleh TDI. Selepas itu., mesin negeri berkembang sehingga ia disusun semula. Langkah seterusnya untuk kebanyakan arahan ialah memilih mod data. Jadi dalam mod ini, data dimuatkan melalui TDI untuk dibaca dari TDO. Untuk TDI & TDO, laluan data akan disusun selaras dengan arahan yang telah dicatatkan. Setelah operasi baca/tulis dilakukan, sekali lagi mesin keadaan berkembang kepada keadaan tetapan semula.

Perbezaan antara JTAG Vs UART

Perbezaan antara JTAG dan UART termasuk yang berikut.

| JTAG |

UART |

| Istilah 'JTAG' bermaksud Kumpulan Tindakan Ujian Bersama. | istilah “ UART ” ialah singkatan kepada Universal Asynchronous Receiver/Transmitter. |

| Ia antara muka segerak yang menggunakan perkakasan terbina untuk pengaturcaraan denyar . | UART ialah antara muka tak segerak yang menggunakan pemuat but yang berjalan dalam memori. |

| Ia ialah satu set port ujian yang digunakan untuk penyahpepijatan tetapi juga boleh digunakan untuk memprogram perisian tegar (yang biasa dilakukan).

|

UART ialah sejenis cip yang mengawal komunikasi ke dan dari peranti, seperti mikropengawal, ROM, RAM, dsb. Selalunya, ia adalah sambungan bersiri yang membolehkan kita berkomunikasi dengan peranti. |

| Ini boleh didapati dalam empat jenis TDI, TDO, TCK, TMS & TRST. | Ini boleh didapati dalam dua jenis UART bodoh & FIFO UART. |

| Kumpulan Tindakan Ujian Bersama ialah pengaturcaraan bersiri atau protokol akses data yang digunakan dalam antara muka mikropengawal & peranti berkaitan. | UART ialah satu jenis cip sebaliknya subkomponen mikropengawal yang digunakan untuk menyediakan perkakasan untuk menjana aliran bersiri tak segerak seperti RS-232/RS-485. |

| Komponen JTAG ialah Pemproses, FPGA, CPLD , dan lain-lain. | Komponen UART ialah penjana CLK, daftar anjakan I/O, hantar atau terima penimbal, penimbal bas data sistem, logik kawalan baca atau tulis, dsb. |

Penganalisis Protokol JTAG

Penganalisis Protokol JTAG seperti PGY-JTAG-EX-PD ialah satu jenis Penganalisis Protokol termasuk beberapa ciri untuk menangkap & menyahpepijat komunikasi di antara hos & reka bentuk yang sedang diuji. Penganalisis jenis ini ialah instrumen utama yang membolehkan jurutera ujian & reka bentuk menguji reka bentuk tertentu JTAG untuk spesifikasinya melalui penyusunan PGY-JTAG-EX-PD seperti Master atau Slave untuk menjana trafik JTAG & menyahkod paket penyahkod bagi Protokol Kumpulan Tindakan Ujian Bersama.

ciri-ciri

Ciri-ciri penganalisis protokol JTAG termasuk yang berikut.

- Ia menyokong sehingga 25MH frekuensi JTAG.

- Ia menjana trafik JTAG & penyahkod protokol untuk Bas secara serentak.

- Ia mempunyai Keupayaan Induk JTAG.

- Kelajuan data JTAG boleh ubah & kitaran tugas.

- Kelewatan TDI & TCK yang ditentukan pengguna.

- Komputer hos antara muka USB 2.0 atau 3.0.

- Analisis Ralat dalam Penyahkodan Protokol

- Protokol menyahkod gambarajah masa bas.

- Penstriman data protokol berterusan ke komputer hos untuk menyediakan penimbal yang besar.

- Senarai aktiviti protokol.

- Pada pelbagai kelajuan, skrip latihan boleh ditulis untuk menggabungkan berbilang penjanaan bingkai data.

Rajah Masa

The gambarajah masa JTAG protokol ditunjukkan di bawah. Dalam rajah berikut, pin TDO kekal dalam keadaan galangan tinggi kecuali semasa keadaan pengawal shift-IR/ shift-DR.

Dalam keadaan pengawal shift-IR & Shift-DR, pin TDO dikemas kini pada tepi menurun TCK melalui Sasaran dan diambil sampel pada kelebihan TCK yang semakin meningkat melalui Hos.

Kedua-dua pin TDI & TMS hanya diambil sampel pada kelebihan TCK yang semakin meningkat melalui Sasaran. Dikemas kini pada kelebihan yang semakin berkurangan sebaliknya TCK melalui Hos.

Aplikasi

The aplikasi JTAG termasuk yang berikut.

- Kumpulan Tindakan Ujian Bersama kerap digunakan dalam Pemproses untuk menyediakan hak kemasukan ke fungsi emulasi atau nyahpepijat mereka.

- Semua CPLD & FPGA menggunakan ini sebagai antara muka untuk memberi akses kepada fungsi pengaturcaraan mereka.

- Ia digunakan untuk ujian PCB tanpa akses fizikal

- Ia digunakan untuk ujian pembuatan peringkat papan.

Oleh itu, ini semua tentang gambaran keseluruhan JTAG – konfigurasi pin, berfungsi dengan aplikasi. JTAG standard industri digunakan untuk pengesahan reka bentuk serta ujian PCB selepas pembuatan. Berikut ialah soalan untuk anda, singkatan JTAG?