ECL (logik gabungan pemancar) pertama kali dicipta di IBM pada Ogos 1956 oleh Hannon S. Yourke. Logik ini juga dikenali sebagai logik mod semasa, digunakan dalam komputer IBM 7090 & 7094. Keluarga ECL sangat pantas berbanding dengan logik digital keluarga. Secara amnya, keluarga logik ini memberikan kelewatan penyebaran kurang daripada 1 ns. Ia adalah keluarga logik berdasarkan transistor simpang bipolar. Ia adalah litar keluarga logik terpantas yang boleh diakses untuk mereka bentuk sistem logik konvensional. Artikel ini membincangkan gambaran keseluruhan a pemancar berganding logik–litar , bekerja dengan aplikasi.

Apakah Logik Berganding Pemancar?

Logik berpasangan pemancar adalah yang terbaik BJT keluarga logik berasaskan yang digunakan dalam reka bentuk sistem logik konvensional. Kadangkala, ia juga dipanggil logik mod semasa yang merupakan teknologi digital berkelajuan tinggi. Secara amnya, ECL dianggap sebagai IC logik terpantas di mana ia mencapai operasi berkelajuan tinggi dengan menggunakan hayunan voltan yang sangat kecil & juga mengelakkan transistor daripada memasuki kawasan tepu.

Pelaksanaan ECL menggunakan voltan bekalan positif yang dikenali sebagai PECL atau ECL rujukan positif. Dalam pintu ECL awal, bekalan voltan negatif digunakan disebabkan oleh imuniti bunyi. Selepas itu, ECL rujukan positif menjadi sangat terkenal kerana tahap logiknya yang lebih serasi berbanding keluarga logik TTL.

Logik bergandingan pemancar menghilangkan sejumlah besar kuasa statik, namun, penggunaan arus keseluruhannya adalah rendah berbanding dengan CMOS pada frekuensi tinggi. Jadi, ECL memberi manfaat terutamanya dalam litar pengedaran jam & aplikasi berasaskan frekuensi tinggi.

Ciri Logik Digabungkan Pemancar

Ciri-ciri ECL akan menjadikannya digunakan dalam banyak aplikasi berasaskan prestasi tinggi.

- ECL menyediakan dua output yang merupakan pelengkap antara satu sama lain sentiasa kerana, pengendalian litar adalah berdasarkan penguat pembezaan.

- Keluarga logik ini terutamanya sesuai untuk kaedah fabrikasi monolitik kerana tahap logik adalah fungsi nisbah perintang.

- Peranti keluarga ECL menjana output yang betul & pelengkap bagi fungsi yang dicadangkan tanpa menggunakan sebarang penyongsang luar. Akibatnya, ia mengurangkan kiraan pakej, dan keperluan kuasa & juga mengurangkan masalah yang berlaku daripada kelewatan masa.

- Peranti ECL dalam reka bentuk penguat pembezaan menawarkan fleksibiliti prestasi yang luas, jadi litar ECL membenarkan digunakan sebagai litar digital dan linear.

- Reka bentuk pintu ECL biasanya mempunyai galangan masukan tinggi & rendah, yang sangat kondusif untuk mencapai keupayaan kipas keluar dan pemacu yang besar.

- Peranti ECL menjana pengaliran arus berterusan pada bekalan kuasa untuk memudahkan reka bentuk bekalan kuasa.

- Peranti ECL termasuk output pemancar terbuka hanya membenarkan mereka memasukkan kapasiti pemacu talian penghantaran.

Litar Logik Berganding Pemancar

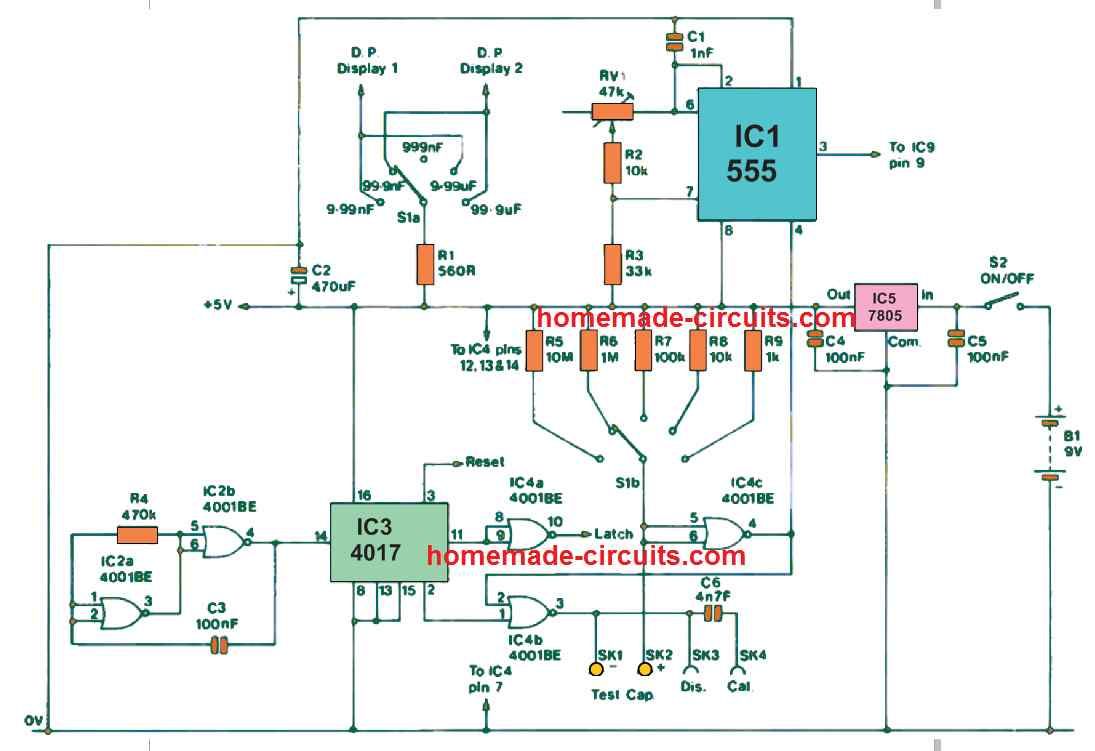

Litar logik bergandingan pemancar untuk penyongsang ditunjukkan di bawah yang direka bentuk dengan perintang dan transistor. Dalam litar ini, terminal pemancar dua transistor hanya disambungkan kepada rintangan menghadkan arus RE yang digunakan untuk mengelakkan transistor daripada memasuki ketepuan. Di sini output transistor diambil dari terminal pengumpul dan bukannya terminal pemancar. Litar ini menyediakan dua output Vout (output terbalik) dan Vout2 (output bukan terbalik) dan terminal input seperti Vin di mana input tinggi atau rendah diberikan. +Vcc = 5V.

Bagaimanakah Logik Gabungan Pemancar Berfungsi?

Operasi logik bergandingan pemancar ialah, apabila input TINGGI diberikan kepada litar ECL, maka ia akan menjadikan transistor ‘Q1’ ON dan transistor Q2 OFF tetapi transistor Q1 tidak tepu. Jadi ini akan menarik keluaran VOUT2 ke TINGGI dan nilai keluaran VOUT1 akan menjadi RENDAH kerana penurunan dalam R1.

Begitu juga apabila nilai VIN yang diberikan kepada ECL adalah LOW, maka ia akan menjadikan transistor Q1 OFF & Q2 transistor ON. Jadi, transistor Q2 tidak akan bergerak ke dalam ketepuan. Jadi ia akan menjadikan output VOUT1 ditarik nilai HIGH dan nilai output VOUT2 akan menjadi rendah kerana penurunan dalam rintangan R2.

Mari lihat bagaimana transistor Q1 dan Q2 dihidupkan dan dimatikan apabila voltan dikenakan.

Kedua-dua transistor seperti Q1 & Q2 dalam litar ini disambungkan sebagai penguat pembezaan oleh perintang pemancar sepunya.

Bekalan voltan untuk litar contoh ini ialah VCC = 5.0, VBB = 4.0 & VEE = 0 V. Nilai peringkat TINGGI & RENDAH input secara ringkas ditakrifkan sebagai 4.4 V & 3.6V. Sebenarnya, litar ini menjana output RENDAH & tahap TINGGI iaitu 0.6 Volt lebih tinggi; bagaimanapun, ini diperbetulkan dalam litar ECL sebenar.

Apabila Vin TINGGI, maka transistor Q1 dihidupkan, namun tidak tepu & transistor Q2 dimatikan. Jadi, voltan keluaran seperti VOUT2 ditarik ke 5 V melalui perintang R2 & boleh ditunjukkan bahawa penurunan voltan merentasi perintang R1 adalah kira-kira 0.8 V supaya VOUT1 = 4.2 V (RENDAH). Selain itu VE = VOUT1 – VQ1 => 4.2V – 0.4V = 3.8V kerana transistor Q1 dihidupkan sepenuhnya.

Sebaik sahaja Vin LOW, transistor Q2 akan dihidupkan, tetapi tidak tepu & transistor Q1 dimatikan. Oleh itu, VOUT1 ditarik ke 5.0 V menggunakan perintang R1 & boleh ditunjukkan bahawa VOUT2 ialah 4.2 V. Juga VE => VOUT2 – VQ2 => 4.2V – 0.8V => 3.4V semasa transistor Q2 dihidupkan.

Dalam ECL, kedua-dua transistor tidak pernah dalam ketepuan sebagai t ayunan voltan input / output agak kecil seperti 0.8v dan impedans input adalah tinggi dan rintangan keluaran adalah rendah. Ini membantu ECL beroperasi dengan lebih pantas dengan masa tunda penyebaran yang lebih sedikit.

Dua Pemancar Masukan Berganding Logik OR/NOR Litar Gerbang

Litar get OR/NOR dua pemancar input logik ditunjukkan di bawah. Litar ini direka bentuk dengan mengubahsuai litar penyongsang di atas. Pengubahsuaian adalah dengan menambah transistor tambahan pada bahagian input.

Kerja litar ini sangat mudah. Apabila input yang digunakan pada kedua-dua transistor Q1 & Q2 adalah rendah maka akan menjadikan output1 (Vout1) kepada nilai TINGGI. Jadi, Vout1 ini sepadan dengan keluaran get NOR.

Pada masa yang sama, jika transistor Q3 dihidupkan, maka ia akan menjadikan output kedua (Vout2) menjadi TINGGI. Jadi, output Vou2 ini sepadan dengan output get OR.

Dengan cara yang sama, jika kedua-dua input transistor Q1 & Q2 adalah TINGGI, maka ia akan menghidupkan transistor Q1 & Q2 dan menyediakan output rendah pada terminal VOUT1.

Jika transistor Q3 dimatikan sepanjang operasi ini maka ia akan memberikan output tinggi pada terminal VOUT2. Jadi, jadual kebenaran untuk get OR/NOR diberikan di bawah.

|

Input |

Input | ATAU |

NOR |

|

A |

B | Y | Y |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Ciri Logik Berganding Pemancar

Ciri-ciri ECL termasuk yang berikut.

- Berbanding dengan TTL, ECL mempunyai masa perambatan yang lebih cepat antara 0.5 hingga 2 ns. Tetapi, pelesapan kuasa logik berganding pemancar adalah lebih tinggi berbanding dengan TTL seperti 30 mW.

- Voltan I/O ECL mempunyai ayunan kecil seperti 0.8.

- Galangan input ECL adalah tinggi & rintangan keluaran adalah rendah; akibatnya, transistor menukar keadaannya dengan cepat.

- Kapasiti kipas keluar ECL adalah tinggi dan kelewatan pintu adalah rendah.

- Logik o/p ECL berubah daripada keadaan RENDAH kepada keadaan TINGGI tetapi tahap voltan untuk keadaan ini akan berbeza antara TTL & EC.

- Imuniti bunyi ECL ialah 0.4V.

Kelebihan dan kekurangan

The kelebihan logik bergandingan pemancar dibincangkan di bawah.

- Fanout ECL ialah 25 yang lebih baik berbanding TTL & ia rendah berbanding CMOS.

- Purata masa tunda penyebaran ECL ialah 1 hingga 4 ns yang lebih baik berbanding kedua-dua CMOS &

- TTL. Oleh itu ia dipanggil sebagai keluarga logik terpantas.

- Apabila BJT dalam pemancar digabungkan gerbang logik bekerja di kawasan aktif, maka mereka mempunyai kelajuan maksimum berbanding dengan semua keluarga logik.

- Gerbang ECL menjana keluaran pelengkap.

- Pancang pensuisan semasa tidak terdapat pada petunjuk bekalan kuasa.

- Output boleh digandingkan bersama untuk menyediakan fungsi berwayar-OR.

- Parameter ECL tidak banyak berubah melalui suhu.

- No. fungsi yang boleh diakses daripada cip sahaja adalah tinggi.

The keburukan logik berganding pemancar dibincangkan di bawah.

- Ia mempunyai margin hingar yang sangat kurang iaitu ±200 mV.

- Pelesapan kuasa adalah tinggi berbanding dengan get logik yang lain.

- Untuk bersambung dengan keluarga logik lain, pengalih tahap diperlukan.

- Fanout mengehadkan pemuatan kapasitif.

- Berbanding dengan TTL , pagar ECL mahal.

- Berbanding dengan CMOS & TTL, imuniti hingar ECL adalah yang paling teruk.

Aplikasi

Aplikasi logik bergandingan pemancar termasuk yang berikut.

- Logik berganding pemancar digunakan sebagai teknologi logik & antara muka dalam peranti komunikasi berkelajuan tinggi seperti antara muka transceiver gentian optik, rangkaian Ethernet & ATM (Mod Pemindahan Asynchronous).

- ECL ialah keluarga logik berdasarkan BJT di mana operasi berkelajuan tingginya boleh dicapai dengan menggunakan hayunan voltan yang agak kecil & mengelakkan transistor daripada bergerak ke kawasan tepu.

- ECL digunakan dalam membuat litar ASLT dalam IBM 360/91.

- ECL mengelakkan penggunaan transistor bertindan dengan menggunakan pincang hujung tunggal i/p & maklum balas positif antara transistor primer & sekunder untuk mencapai fungsi penyongsang.

- ECL digunakan dalam elektronik berkelajuan tinggi.

Oleh itu, ini adalah gambaran keseluruhan logik berganding pemancar atau ECL – litar, kerja, ciri, ciri dan aplikasi. ECL adalah keluarga logik terpantas berdasarkan BJT berbanding keluarga logik digital lain. Ia mencapai operasi kelajuan maksimumnya dengan menggunakan hayunan voltan kecil & mengelakkan transistor daripada bergerak ke kawasan tepu. Keluarga logik ini memberikan kelewatan pembiakan 1ns yang luar biasa dan dalam keluarga ECL terkini, kelewatan ini berkurangan. Berikut adalah soalan untuk anda, apakah nama alternatif untuk ECL?