Transistor unijunction adalah peranti semikonduktor terminal 3 yang tidak seperti BJT yang hanya mempunyai satu persimpangan pn. Ia pada dasarnya dirancang untuk digunakan sebagai litar pengayun satu peringkat untuk menghasilkan isyarat berdenyut yang sesuai untuk aplikasi litar digital.

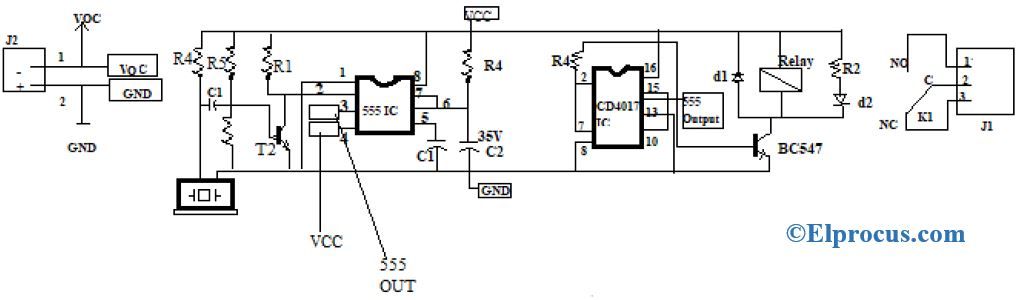

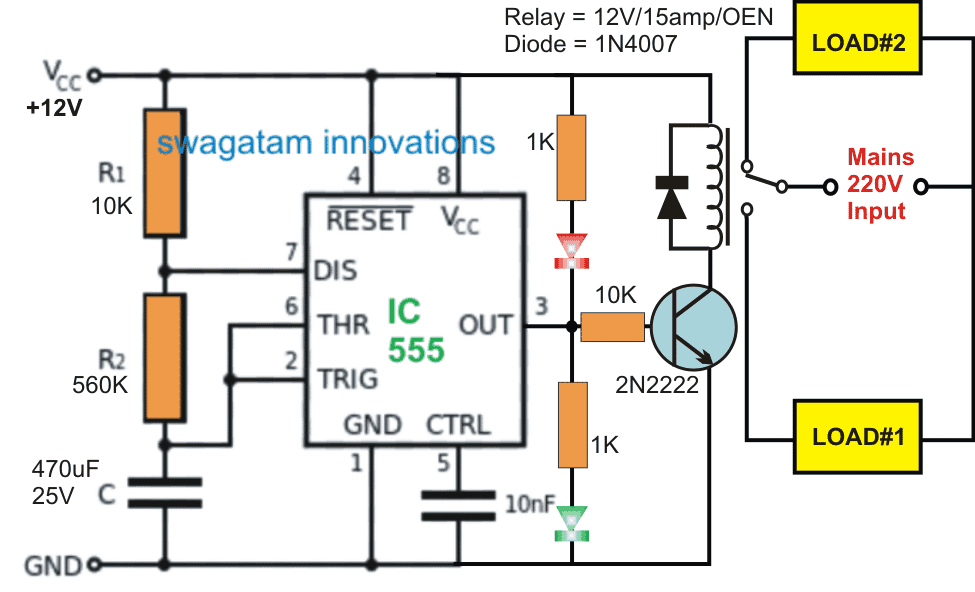

Litar Osilator Relaksasi UJT

Transistor unjungsi biasanya boleh dikabelkan dalam bentuk pengayun relaksasi seperti yang ditunjukkan dalam litar asas berikut.

Di sini komponen RT dan CT berfungsi seperti elemen pemasa dan menentukan frekuensi atau kadar ayunan litar UJT.

Untuk mengira frekuensi berayun kita dapat menggunakan formula berikut, yang menggabungkan nisbah tegakan intrinsik transistor unijunction yang sebagai salah satu parameter bersama dengan RT dan CT untuk menentukan denyutan berayun.

Nilai standard nisbah stand-off untuk peranti UJT biasa adalah antara 0.4 dan 0.6 . Oleh itu mempertimbangkan nilai yang = 0.5, dan menggantikannya dalam persamaan di atas kita dapat:

Apabila bekalan dihidupkan, voltan melalui perintang RT mengenakan kapasitor CT ke arah tahap bekalan VBB. Sekarang, voltan tegakan mati ditentukan oleh Vp merentasi B1 - B2, bersamaan dengan nisbah tegakan UJT yang sebagai: Vp = yang VB1VB2 - VD.

Sejak sekian lama voltan VE merentasi kapasitor tetap lebih rendah daripada Vp, terminal UJT merentasi B1, B2 menunjukkan litar terbuka.

Tetapi ketika voltan merentasi CT melampaui Vp, transistor unjungsi menyala, melepaskan kapasitor dengan cepat, dan memulakan kitaran baru.

Semasa kejadian tembakan UJT, menyebabkan potensi di seluruh R1 naik, dan potensi di seluruh R2 untuk turun.

Bentuk gelombang yang dihasilkan di seluruh pemancar UJT menghasilkan isyarat gigi gergaji, yang menunjukkan potensi arah positif di B2, dan potensi arah negatif pada petunjuk B1 UJT

Kawasan Aplikasi Transistor Unijunction

Berikut adalah kawasan aplikasi utama di mana transistor unijunction digunakan secara meluas.

- Litar Pencetus

- Litar Pengayun

- Bekalan voltan / semasa yang dikawal.

- Litar berdasarkan pemasa,

- Penjana Sawtooth,

- Litar Kawalan Fasa

- Rangkaian bistable

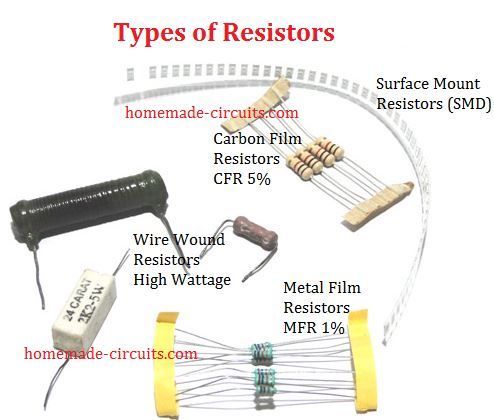

Ciri-ciri utama

Mudah Diakses dan Murah : Harga yang murah dan kemudahan penggunaan UJT bersama dengan beberapa ciri yang luar biasa telah menyebabkan pelaksanaan peranti ini secara meluas dalam banyak aplikasi elektronik.

Penggunaan Kuasa Rendah : Kerana fitur penggunaan tenaga yang rendah dalam keadaan kerja normal, perangkat ini dianggap sebagai penembusan luar biasa dalam usaha berterusan untuk mengembangkan peranti yang cukup efisien.

Operasi Boleh dipercayai yang sangat stabil : Apabila digunakan sebagai pengayun atau litar pencetus kelewatan, UJT berfungsi dengan kebolehpercayaan yang melampau dan dengan tindak balas output yang sangat tepat.

Pembinaan Asas Transistor Unijunction

Rajah 1

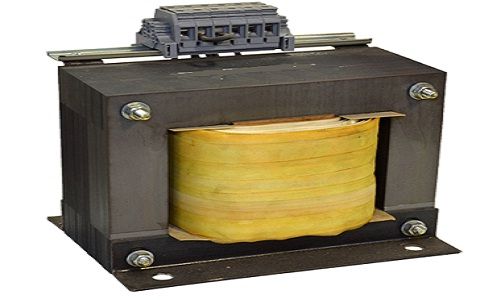

UJT adalah peranti semikonduktor tiga terminal yang menggabungkan pembinaan sederhana seperti yang digambarkan dalam gambar di atas.

Dalam pembinaan ini, sekatan bahan silikon jenis-n yang agak lemah (mempunyai ciri rintangan yang meningkat) menyediakan sepasang kenalan asas yang disambungkan ke dua hujung satu permukaan, dan batang aluminium yang disatukan pada permukaan belakang yang bertentangan.

Persimpangan p-n peranti dibuat di sempadan batang aluminium dan blok silikon jenis-n.

Persimpangan p-n tunggal yang terbentuk ini adalah alasan untuk nama peranti 'unijunction' . Peranti ini pada mulanya dikenali sebagai diod asas duo (berganda) kerana berlakunya sepasang kenalan asas.

Perhatikan bahawa pada gambar di atas bahawa batang aluminium disatu / digabungkan pada blok silikon pada kedudukan yang lebih dekat dengan hubungan asas 2 daripada hubungan asas 1, dan juga terminal asas 2 telah menjadi positif berkenaan dengan terminal asas 1 oleh volt VBB. Bagaimana aspek-aspek ini mempengaruhi cara kerja UJT akan dapat dilihat pada bahagian berikut

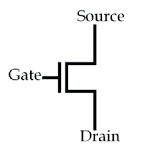

Perwakilan Simbolik

Perwakilan simbolik transistor unijunction dapat dilihat pada gambar di bawah.

Gambar # 2

Perhatikan bahawa terminal pemancar ditunjukkan dengan sudut ke garis lurus yang menggambarkan blok bahan jenis-n. Kepala anak panah dapat dilihat mengarah ke arah arus arus (lubang) khas sementara perangkat unijungsi berada dalam keadaan bias ke depan, dipicu, atau konduktif.

Litar Setara Transistor Unijunction

Gambar # 3

Litar UJT yang setara dapat dilihat pada gambar yang ditunjukkan di atas. Kita dapat mengetahui betapa mudahnya litar setara ini, yang merangkumi beberapa perintang (satu tetap, satu laras) dan satu diod bersendirian.

Rintangan RB1 dipaparkan sebagai perintang yang boleh disesuaikan memandangkan nilainya akan berubah seiring perubahan arus IE. Sebenarnya, dalam mana-mana transistor yang mewakili unijungsi, RB1 boleh turun naik dari 5 kΩ hingga 50 Ω untuk sebarang perubahan setara IE dari 0 hingga 50 = μA. Rintangan interbase RBB mewakili rintangan peranti antara terminal B1 dan B2 apabila IE = 0. Dalam formula untuk ini adalah,

RBB = (RB1 + RB2) | IE = 0

Julat RBB biasanya dalam lingkungan 4 dan 10 k. Penempatan batang aluminium seperti yang ditunjukkan pada gambar pertama memberikan magnitud relatif RB1, RB2 ketika IE = 0. Kita dapat menganggarkan nilai VRB1 (ketika IE = 0) menggunakan hukum pembahagi voltan, seperti yang diberikan di bawah:

VRB1 = (RB1 x VBB) / (RB1 + RB2) = ηVBB (dengan IE = 0)

Surat Yunani yang (eta) dikenali sebagai nisbah penutupan intrinsik peranti transistor unijunction dan ditakrifkan oleh:

η = RB1 / (RB1 + RB2) (dengan IE = 0) = RB1 / RBB

Untuk voltan pemancar yang ditunjukkan (VE) lebih tinggi daripada VRB1 (= ηVBB) oleh penurunan voltan hadapan diod VD (0.35 → 0.70 V), dioda akan dipicu ON. Sebaik-baiknya kita menganggap keadaan litar pintas, sehingga IE akan mula bergerak melalui RB1. Melalui persamaan, tahap voltan pemicu pemancar dapat dinyatakan sebagai:

VP = ηVBB + VD

Ciri-ciri Utama dan Berfungsi

Ciri-ciri transistor unijungsi perwakilan untuk VBB = 10 V ditunjukkan dalam gambar di bawah.

Gambar # 4

Kita dapat melihat bahawa, untuk potensi pemancar yang ditunjukkan di sebelah kiri titik puncak, nilai IE tidak pernah melebihi IEO (yang berada dalam mikroamper). IEO semasa lebih kurang mengikuti ICO arus kebocoran terbalik transistor bipolar konvensional.

Wilayah ini, disebut sebagai daerah pemotongan, seperti juga ditunjukkan dalam gambar.

Sebaik sahaja konduksi dicapai pada VE = VP, potensi pemancar VE menurun seiring peningkatan potensi IE, yang tepat sesuai dengan penurunan rintangan RB1 untuk meningkatkan IE arus, seperti yang dijelaskan sebelumnya.

Ciri di atas menyediakan transistor unijungsi dengan kawasan rintangan negatif yang sangat stabil, yang membolehkan peranti berfungsi dan digunakan dengan kebolehpercayaan yang melampau.

Selama proses di atas, titik lembah diharapkan dapat dicapai akhirnya, dan setiap kenaikan IE di luar julat ini menyebabkan perangkat memasuki wilayah tepu.

Rajah # 3 menunjukkan litar setara diod di rantau yang sama dengan pendekatan ciri yang serupa.

Penurunan nilai rintangan peranti di kawasan aktif disebabkan oleh lubang yang disuntik ke dalam blok jenis-n oleh batang aluminium jenis-p sebaik penembakan peranti berlaku. Ini mengakibatkan peningkatan kuantiti lubang pada bahagian jenis-n meningkatkan bilangan elektron bebas, menyebabkan kekonduksian yang ditingkatkan (G) di seluruh peranti dengan penurunan ketahanannya yang setara (R ↓ = 1 / G ↑)

Parameter Penting

Anda akan menemui tiga parameter penting tambahan yang dikaitkan dengan transistor unijunction iaitu IP, VV, dan IV. Semua ini ditunjukkan dalam gambar # 4.

Ini sebenarnya agak mudah difahami. Ciri pemancar yang sedia ada dapat dipelajari dari gambar # 5 di bawah.

Gambar # 5

Di sini kita dapat melihat bahawa IEO (μA) tidak dapat diperhatikan kerana skala mendatar dikalibrasi dalam miliamper. Setiap lengkung yang bersilang dengan paksi menegak adalah hasil yang sama dari VP. Untuk nilai tetap η dan VD, nilai VP berubah sesuai dengan VBB, seperti yang dirumuskan di bawah:

Lembaran Data Transistor Unijunction

Pelbagai spesifikasi teknikal standard untuk UJT dapat dipelajari dari Gambar # 5 di bawah.

Maklumat Pinout UJT

Perincian pinout juga disertakan dalam lembar data di atas. Perhatikan bahawa terminal asas B1 dan B2 terletak bertentangan antara satu sama lain sementara pemancar pin ADALAH diletakkan di tengah, antara kedua-duanya.

Lebih-lebih lagi, pin asas yang seharusnya dihubungkan dengan tahap bekalan yang lebih tinggi terletak berhampiran dengan pemotretan di kolar bungkusan.

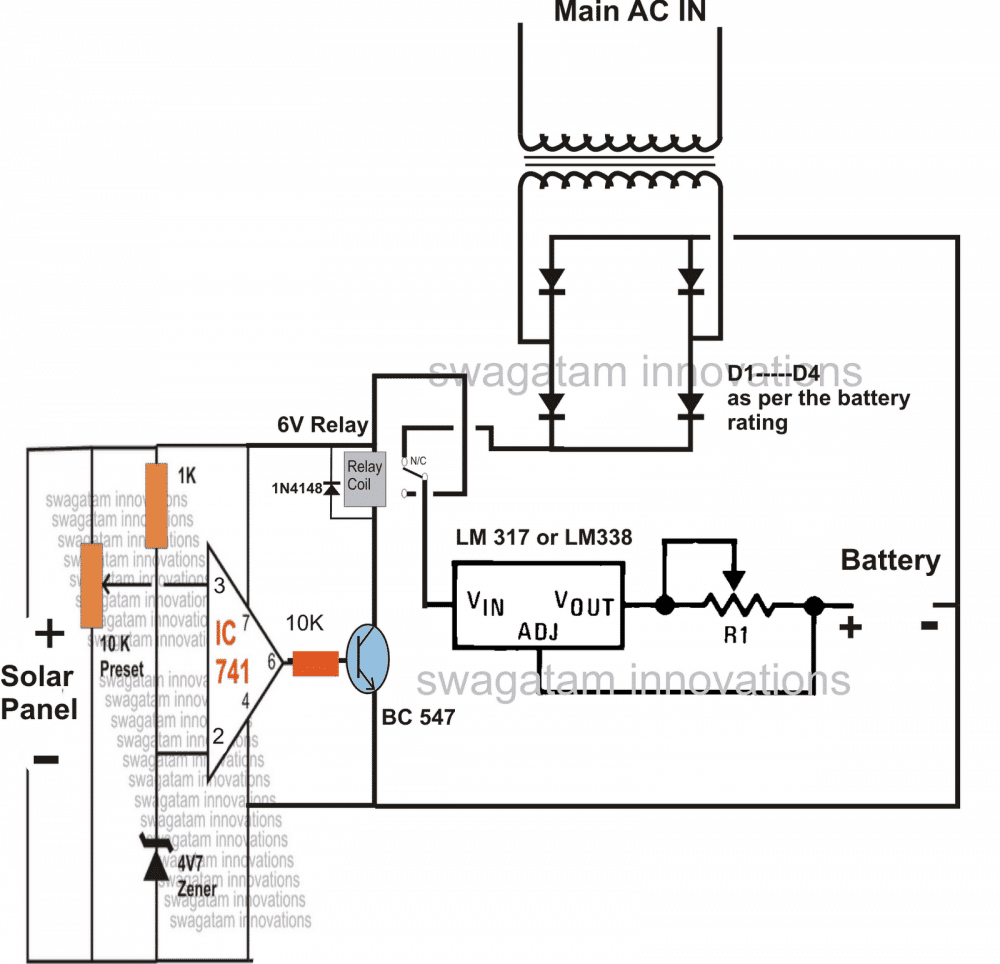

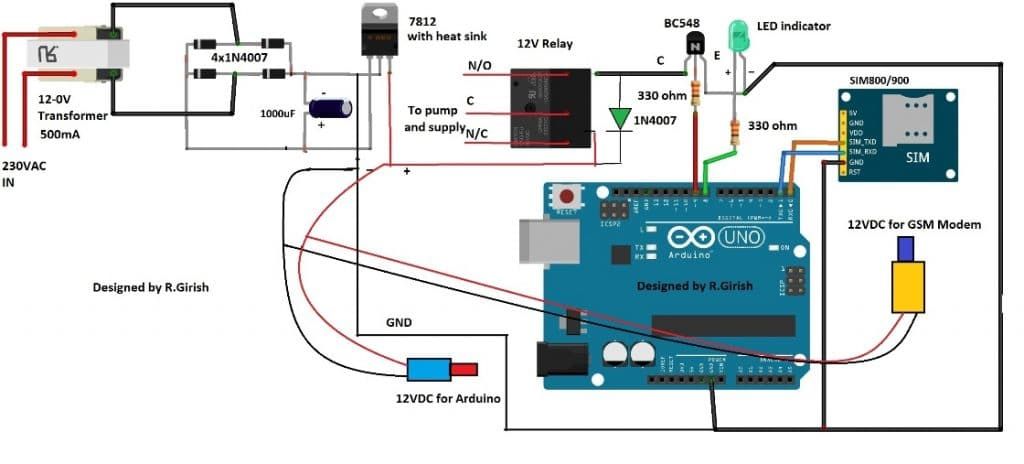

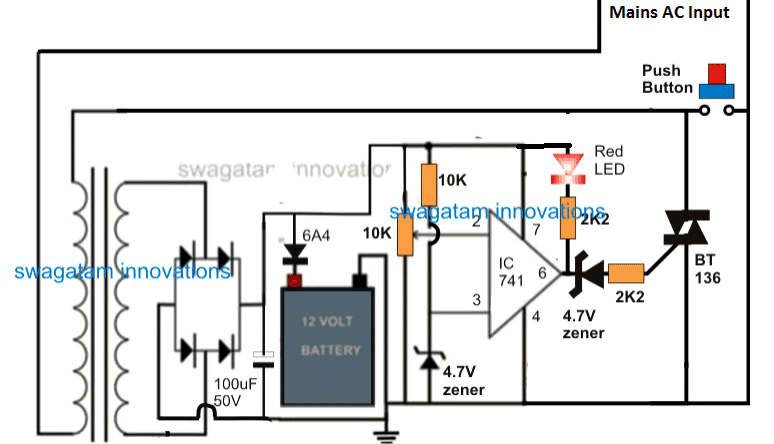

Cara menggunakan UJT untuk Mencetuskan SCR

Salah satu aplikasi UJT yang agak popular adalah untuk mencetuskan peranti kuasa seperti SCR. Komponen asas litar pemicu jenis ini digambarkan dalam rajah # 6 yang ditunjukkan di bawah.

Gambar # 6: Mencetuskan SCR menggunakan UJT

Gambar # 7: Garis beban UJT untuk pencetus untuk peranti luaran seperti SCR

Komponen pemasa utama dibentuk oleh R1 dan C, sementara R2 berfungsi seperti resistor tarik turun untuk voltan pencetus output.

Cara Mengira R1

Perintang R1 harus dihitung untuk menjamin bahawa garis beban seperti yang didefinisikan oleh R1 bergerak melalui ciri-ciri peranti di dalam rintangan negatif, yang bermaksud, ke arah kanan titik puncak tetapi ke sisi kiri titik lembah seperti yang ditunjukkan dalam Gambar # 7.

Sekiranya garis beban tidak dapat melintasi sisi kanan titik puncak, peranti unijunction tidak dapat dimulakan.

Rumus R1 yang menjamin keadaan beralih ON dapat ditentukan setelah kita mempertimbangkan titik puncak di mana IR1 = IP dan VE = VP. Persamaan IR1 = IP kelihatan logik kerana arus pengisian kapasitor, pada ketika ini, adalah sifar. Maksudnya, kapasitor pada titik spesifik ini bergerak melalui pengisian ke keadaan pemakaian.

Oleh itu, untuk keadaan di atas, kita boleh menulis:

Sebagai alternatif, untuk menjamin pemadaman SCR yang lengkap:

R1> (V - Vv) / Iv

Ini menunjukkan bahawa julat pemilihan perintang R1 harus dinyatakan seperti yang diberikan di bawah:

(V - Vv) / Iv

Cara Mengira R2

Perintang R2 mestilah cukup kecil untuk memastikan bahawa SCR tidak dipicu secara salah oleh voltan VR2 merentasi R2 ketika IE ≅ 0 Amp. Untuk ini VR2 mesti dikira mengikut formula berikut:

VR2 ≅ R2V / (R2 + RBB) (ketika IE ≅ 0)

Kapasitor memberikan kelewatan masa antara nadi pencetus, dan juga menentukan panjang setiap nadi.

Cara Mengira C

Merujuk pada gambar di bawah ini, sebaik sahaja litar dihidupkan, voltan VE yang sama dengan VC akan mula mengecas kapasitor ke voltan VV, melalui pemalar masa τ = R1C.

Gambar # 8

Persamaan umum yang menentukan tempoh pengisian C dalam rangkaian UJT adalah:

vc = Vv + (V - Vv) (1 - adalah-t / R1C)

Melalui pengiraan sebelumnya, kita sudah mengetahui voltan merentasi R2 semasa tempoh pengisian kapasitor di atas. Sekarang, apabila vc = vE = Vp, peranti UJT akan masuk ke keadaan ON ON, menyebabkan kapasitor melepaskan melalui RB1 dan R2, dengan kadar bergantung pada pemalar waktu:

τ = (RB1 + R2) C

Persamaan berikut boleh digunakan untuk mengira masa pelepasan bila

vc = vE

anda ≅ Vpe -t / (RB1 + R2) C

Persamaan ini telah berubah menjadi agak rumit disebabkan oleh RB1, yang mengalami penurunan nilai ketika arus pemancar meningkat, bersama dengan aspek lain dalam litar seperti R1 dan V, yang juga mempengaruhi kadar pelepasan C secara keseluruhan.

Walaupun demikian, jika kita merujuk pada rangkaian setara seperti yang diberikan di atas Gambar # 8 (b), biasanya nilai R1 dan RB2 dapat sedemikian rupa sehingga jaringan Thévenin untuk konfigurasi di sekitar kapasitor C mungkin sedikit terpengaruh oleh R1, Perintang RB2. Walaupun voltan V nampaknya agak besar, pembahagi resistif yang membantu voltan Thévenin secara umum dapat diabaikan dan dihilangkan, seperti yang ditunjukkan dalam rajah setara yang dikurangkan di bawah:

Oleh itu, versi ringkas di atas membantu kita mendapatkan persamaan berikut untuk fasa pelepasan kapasitor C, ketika VR2 berada di puncaknya.

VR2 ≅ R2 (Vp - 0.7) / R2 + RB1

Untuk lebih banyak litar aplikasi, anda juga boleh rujuk artikel ini

Sebelumnya: Litar Pemancar Mini Seterusnya: Litar Penggera Pencuri PIR