Istilah VLSI bermaksud 'Teknologi Integrasi Skala Sangat Besar' yang melibatkan merancang litar bersepadu (IC) dengan menggabungkan ribuan transistor secara logik menjadi satu cip oleh litar logik yang berbeza . IC ini akhirnya mengurangkan ruang litar yang dihuni jika dibandingkan dengan litar dengan IC konvensional. Kuasa komputasi dan penggunaan ruang adalah cabaran utama reka bentuk VLSI. Melaksanakan projek VLSI membuka kerjaya yang mencabar dan cerah bagi pelajar dan juga penyelidik. Beberapa kawasan tren baru VLSI adalah Array Gerbang diprogramkan di lapangan aplikasi (FPGA), reka bentuk ASIC, dan SOC. Senarai beberapa projek VLSI diberikan di bawah untuk para pelajar yang bersungguh-sungguh mencari projek dalam bidang ini. Artikel ini membincangkan gambaran keseluruhan projek VLSI berdasarkan FPGA, Xilinx, IEEE, Mini, Matlab, dan lain-lain disenaraikan di bawah. Projek-projek ini sangat membantu pelajar kejuruteraan, pelajar M.tech.

Projek VLSI untuk Pelajar Kejuruteraan

Projek VLSI dengan abstrak untuk pelajar kejuruteraan elektronik dibincangkan di bawah.

Projek VLSI

1). Transformasi Discrete Wavelet berdasarkan 3D Lifting

Projek ini membantu dalam menyediakan gambar yang sangat tepat dengan menggunakan pengekodan gambar tanpa kehilangan datanya. Untuk mencapainya, proses ini menerapkan penapis pengangkat bergantung pada transformasi seni bina 3D Wavelet diskrit VLSI.

2). Merancang Pengganda SFQ dengan 4-bit dengan Berkesan melalui Perkakasan Berkelajuan Tinggi

Projek ini digunakan terutamanya untuk melaksanakan encoder booth yang diubah (MBE) dengan SFQ berasaskan 4-bit pengganda . Pengganda ini memberikan prestasi yang baik jika dibandingkan dengan encoder booth konvensional. Projek ini digunakan terutamanya dalam aplikasi kelewatan kritikal.

3). Pemproses Kriptografi yang digunakan dalam Kad Pintar dengan Kawasan yang Efisien

Projek ini digunakan untuk melaksanakan tiga algoritma kriptografi yang disokong oleh kunci peribadi & awam yang digunakan dalam kad pintar aplikasi untuk memberikan pengesahan & data pengguna yang sangat selamat komunikasi .

4). Pengganda Berkelajuan Tinggi atau Daya Rendah dengan Kaedah Penekanan Kuasa Tersembunyi

Sistem yang dicadangkan ini menyaring isyarat palsu aritmetik yang tidak berguna untuk mengelakkan penghantaran data yang tidak perlu yang tidak mempengaruhi hasil pengkomputeran terakhir. Sistem ini menggunakan kaedah SPST untuk pengganda untuk mencapai penghantaran kuasa rendah dan berkelajuan tinggi.

5). Pemampatan & Penyahmampatan Algoritma Data Tanpa Kehilangan

Projek ini dilaksanakan terutamanya untuk seni bina perkakasan 2 peringkat bergantung pada ciri algoritma PDLZW (Parallel Dictionary LZW) serta algoritma jenis Adaptive Huffman yang digunakan untuk kedua-dua aplikasi pemampatan data tanpa kerugian & penyahmampatan tanpa kerugian.

6). Senibina Turbo Decoder dengan Kerumitan Rendah untuk WSN Berkekuatan Tenaga

Sistem yang dicadangkan digunakan untuk mengurangkan jumlah penggunaan tenaga sepanjang penghantaran data WSN melalui algoritma penguraian LUT-Log-BCJR ke operasi ACS asas (Tambah Bandingkan Pilih).

7). Senibina VLSI untuk Menghilangkan Kebisingan Impuls Gambar dengan Cekap

Sistem yang dicadangkan ini digunakan terutamanya untuk meningkatkan kualiti gambar secara visual untuk mengelakkan kemungkinan rosak dengan bunyi impuls untuk menerapkan seni bina VLSI yang efisien dengan bantuan penapis pemeliharaan tepi.

8). Senibina Pemproses Dalam Memori yang digunakan untuk Pemampatan Multimedia

Sistem yang dicadangkan ini memberikan seni bina kerumitan rendah untuk pemproses dalam ingatan untuk menyokong aplikasi multimedia iaitu pemampatan gambar, video melalui penggunaan arahan tunggal yang besar, pelbagai konsep data & kata arahan.

9). Teknik Penyegerakan Masa dengan Kadar Simbol untuk Sistem OFDM Tanpa Wayar dengan Kuasa Rendah

Sistem yang dicadangkan ini digunakan terutamanya untuk meningkatkan tindakan OFDM tanpa wayar (Bahagian Frekuensi Ortogonal Pelbagai mod ) sistem melalui penurunan kuasa keseluruhan baseband dengan bantuan jam penjana dengan pengawal masa-sampel fasa & dinamik fasa.

10). Pelaksanaan Pengganda Daya Rendah & Berkelajuan Tinggi berasaskan Accumulator dengan SPST Adder & Verilog

Projek ini digunakan untuk merancang MAC berkekuatan rendah & berkelajuan tinggi (pengganda dan penumpuk) dengan menerima kaedah penekanan kuasa yang salah pada MBE (encoder booth yang diubah). Dengan menggunakan reka bentuk ini, pelesapan kuasa dari keseluruhan pensuisan dapat dielakkan.

11). Reka Bentuk & Pelaksanaan Pemproses Robot dengan Mengaktifkan Perlanggaran dengan Teknologi RFID

Sistem yang dicadangkan digunakan terutamanya untuk melaksanakan pemproses robot dengan anti-perlanggaran untuk mengelakkan perlanggaran robot secara fizikal di persekitaran multi-robot. Algoritma ini dilaksanakan terutamanya menggunakan teknologi VHDL & RFID.

12). Merancang Litar Logik dengan Tenaga Cekap menggunakan Kaedah Adiabatik

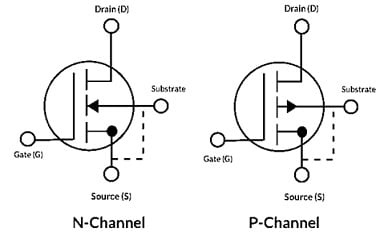

Sistem ini menunjukkan reka bentuk litar logik dengan cekap dengan kaedah adiabatik jika dibandingkan melalui reka bentuk CMOS konvensional dengan bantuan litar menggunakan Gerbang NAND & NOR . Dengan menggunakan kaedah adiabatik, penghilangan daya dalam rangkaian dapat dikurangkan serta mengitar semula tenaga yang tersimpan di dalam kapasitor beban.

3). Sistem Penyulitan untuk Meningkatkan Kelajuan Pengkomputeran Sistem

Tujuan utama projek ini adalah untuk meningkatkan keselamatan penghantaran data untuk meningkatkan kelajuan pengkomputeran dengan menerapkan algoritma AES menggunakan FPGA. Jadi, simulasi ini, serta reka bentuk matematik, dapat dijalankan dengan bantuan kod VHDL.

14). Blok IP AHM atau Bas Berprestasi Tinggi Lanjutan

Projek ini digunakan terutamanya untuk merancang seni bina Advanced Pengawal mikro Bas (AMB) dengan menggunakan AHBN (Bas Berprestasi Tinggi Lanjutan). Projek ini boleh dirancang dengan kod VHDL dengan melaksanakan blok seperti master & save.

15). Pemancar RF Multimode berasaskan DSM dengan Multichannel

Sistem ini terutama digunakan untuk merancang arsitektur pemancar & penerima multimode dan multichannel RF dengan modulator Delta-Sigma. Sistem yang dicadangkan ini menggunakan bahasa VHDL untuk melaksanakan dua seni bina.

16). The Concentrator of Knockout Switch menggunakan Mod Pemindahan Asinkron

Dengan menggunakan projek ini, suis kalah mati berdasarkan pemindahan tak segerak dapat dirancang dengan bantuan alat seperti VHS & VHDL. Suis kalah mati ini dapat digunakan dalam rangkaian paket litar maya dan juga aplikasi datagram.

17). Sintesis Tingkah Laku Litar Asinkron

Projek ini digunakan terutamanya untuk menyediakan teknik sintesis tingkah laku yang digunakan untuk litar tak segerak. Kedua-dua templat seperti implementasi balsa & asynchronous adalah elemen utama dalam reka bentuk.

18). Reka bentuk AMBA menggunakan Pengawal Memori yang Sesuai dengan AHB

Projek ini digunakan untuk merancang MC (memory controller) bergantung pada AMBA (Advanced Microcontroller Bus Architecture) untuk pengendalian memori sistem menggunakan memori utama seperti SRAM & ROM.

19). Pelaksanaan Carry Tree Adder

Carry tree adder berdasarkan reka bentuk VLSI disebut sebagai penambah prestasi terbaik berbanding dengan penambah binari biasa. Penambah yang dilaksanakan oleh projek ini adalah pohon span, batu kogge, dan batu kogge jarang.

20). Reka bentuk CORDIC Putaran Sudut Tetap

Konsep utama sistem yang dicadangkan ini ialah menghidupkan vektor menggunakan sudut tetap. Sudut ini diperlukan untuk permainan, robotik, pemprosesan imej , dll. Dengan menggunakan projek ini, putaran vektor dapat dicapai dengan menggunakan sudut tertentu dengan reka bentuk CORDIC (komputer digital putaran koordinat).

21). Reka Bentuk Penapis FIR dengan Aritmetik Taburan Carian Teragih

Sistem yang dicadangkan ini terutamanya meningkatkan Penapis FIR prestasi dengan merancangnya menggunakan aritmetik diedarkan dari jadual carian 3 dimensi sebagai pengganti pengganda. Jadi reka bentuk ini dapat dilaksanakan dengan menggunakan perisian seperti FPGA & Xilinx.

22). Patch-Pulled Patched Latches with High Speed & Low Power Bersyarat

Projek ini digunakan untuk melaksanakan kait berdenyut cekap tenaga & berprestasi tinggi yang digunakan terutamanya untuk sistem VLSI dengan menggunakan topologi baru. Kerana topologi ini bergantung terutamanya pada push-pull tahap akhir yang digerakkan menggunakan dua jalur pemisah melalui penjana denyut bersyarat.

23). Aritmetik Coder VLSI Architecture dalam SPIHT

Sistem yang dicadangkan ini meningkatkan throughput kaedah pengekodan aritmetik dalam pemisahan set dalam pemampatan gambar pokok hierarki (SPIHT) dengan seni bina berkelajuan tinggi bergantung pada FPGA.

24). Kebisingan Penindasan Isyarat ECG berdasarkan FPGA

Projek ini digunakan untuk menahan kebisingan dalam isyarat ECG melalui dua penapis median dengan ukuran titik sampel 91 & 7 masing-masing. Jadi proses ini dapat dicapai dengan melaksanakan Reka bentuk FPGA berdasarkan kod VHDL.

25). Pemproses Skala Imej Berprestasi Tinggi berasaskan VLSI dengan Kos Rendah

Projek ini digunakan untuk menerapkan algoritma pemproses penskalaan gambar berdasarkan VLSI dengan memori yang kurang dan prestasi tinggi. Reka bentuk sistem yang dicadangkan terutamanya mengandungi gabungan penapis, kaedah dinamik yang dapat dikonfigurasi ulang & perkongsian perkakasan untuk mengurangkan kos.

26). Reka Bentuk & Pelaksanaan Senibina Array Systolic dengan cekap

Konsep utama projek ini adalah untuk merancang model perkakasan yang digunakan untuk pengganda array sistolik. Susunan ini boleh digunakan terutamanya untuk melakukan pendaraban binari dengan bantuan platform VHDL. Reka bentuk sistem yang dicadangkan dapat dilaksanakan dengan menggunakan perisian FPGA & Isim.

27). Reka Bentuk & Sintesis QPSK menggunakan Kod VHDL

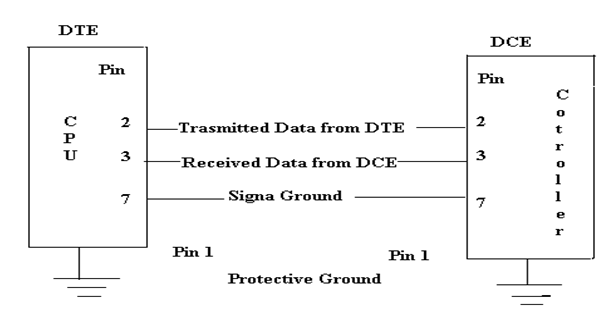

QPSK adalah salah satu kaedah modulasi utama. Kaedah ini digunakan dalam aplikasi radio satelit. Teknik modulasi ini dapat dilaksanakan melalui gerbang logik terbalik. Perancangan teknik QPSK dapat dilakukan dengan bantuan kod VHDL.

28). Reka Bentuk & Pelaksanaan Pengendali DDR SDRAM dengan Kelajuan Tinggi

Sistem yang dicadangkan digunakan untuk merancang pengawal SDDR DDR untuk memindahkan data pecah bergantung pada kecepatan tinggi untuk menyegerakkan data ini di antara rangkaian sistem tertanam & DDR SDRAM. Dengan menggunakan bahasa VHDL, kodnya dapat dikembangkan.

29). Reka Bentuk & Pelaksanaan Prosesor RISC 32 Â-bit

Konsep utama projek ini adalah melaksanakan 32 bit RISC (Komputer Set Arahan Berkurang) dengan bantuan alat seperti XILINK VIRTEX4. Dalam projek ini, 16 set arahan dirancang di mana sahaja setiap arahan dapat dilaksanakan dalam satu siklus CLK menggunakan kaedah pipelining lima fasa.

30). Pelaksanaan Jambatan Bas antara AHB & OCP

Sistem yang dicadangkan digunakan untuk merancang jambatan bas antara dua protokol iaitu common & standard. Protokol komunikasi seperti AHB (Advanced High-Performance Bus) & OCP (Open Core Protocol) sangat popular yang digunakan dalam aplikasi SoC (Sistem On-chip) .

Idea Projek VLSI untuk Pelajar Kejuruteraan

Senarai projek VLSI berdasarkan FPGA, MatLab, IEEE, dan Projek Mini untuk pelajar kejuruteraan disenaraikan di bawah.

Projek VLSI untuk Pelajar M. Tech

Senarai projek VLSI berdasarkan M. Tech Pelajar merangkumi yang berikut.

- Reka Bentuk Sel Memori I0T berasaskan RHBD yang Efisien & Sangat Boleh dipercayai yang digunakan dalam Aplikasi Aeroangkasa

- Pengesan Fasa dengan Kadar Separuh Bertingkat yang digunakan untuk Litar Pemulihan CLK & Data

- Pembanding dengan Daya Rendah & Kelajuan Tinggi yang digunakan untuk Aplikasi Tepat

- Penterjemah Tahap Voltan Berpagar dengan Multiplexer Berprestasi Tinggi & Bersepadu

- Ternary Adder berasaskan CNTFET dengan Prestasi Tinggi

- Reka Bentuk Magnitud Pembanding dengan Kuasa Rendah

- Reka Bentuk Pintu Logik Ambang dengan Mod Semasa untuk Analisis Kelewatan

- Reka Bentuk Penyahkod Garis Logik Campuran dengan Tenaga Rendah & Berprestasi Tinggi

- Reka Bentuk Kebolehpercayaan Logik Konvensyen Tidur

- Pengubah Tahap Voltan untuk Aplikasi Bekalan Dwi dengan Kelajuan Tinggi & Berkekuatan Kuasa

- Reka Bentuk & Analisis Perbandingan Double-Tail Daya Rendah & Voltan Rendah

- Reka Bentuk Flip-Flop berdasarkan Pulse-Triggered dengan Daya Rendah menggunakan Kaedah Isyarat Umpan

- Reka Bentuk Litar yang Efisien berdasarkan FET yang Boleh dikonfigurasi Runtime

- Reka Bentuk Magnitud Pembanding dengan Kuasa Rendah

- Analisis Kelewatan Reka Bentuk Logik Pintu dengan Ambang Mod Semasa

The Projek VLSI berasaskan FPGA untuk pelajar kejuruteraan dan Projek mini reka bentuk CMOS VLSI disenaraikan di bawah.

- Reka Bentuk & Pencirian Litar Keras SEU untuk FPGA berdasarkan SRAM

- Aplikasi Reka Bentuk & Potensi hibrid CMOS hybrid berasaskan Compact Memristor yang digunakan dalam FPGA

- Pelaksanaan FPGA berdasarkan Sensor Ultrasonik untuk Pengukuran Jarak

- Pelaksanaan FPGA untuk Booth Multiplier dengan Spartan6 FPGA

- Transformasi Wavelet Diskrit berdasarkan Mengangkat dengan Spartan3 FPGA

- Pengawal ARM dalam Robotik menggunakan FPGA

- UART berasaskan FPGA dengan Multichannel

- Penindasan Kebisingan Isyarat EKG menggunakan FPGA

- Pelaksanaan FPGA berasaskan UTMI & Lapisan Protokol USB 2.0

- Pelaksanaan Median Filter dengan Spartan3 FPGA

- Pelaksanaan FPGA berdasarkan Algoritma AES

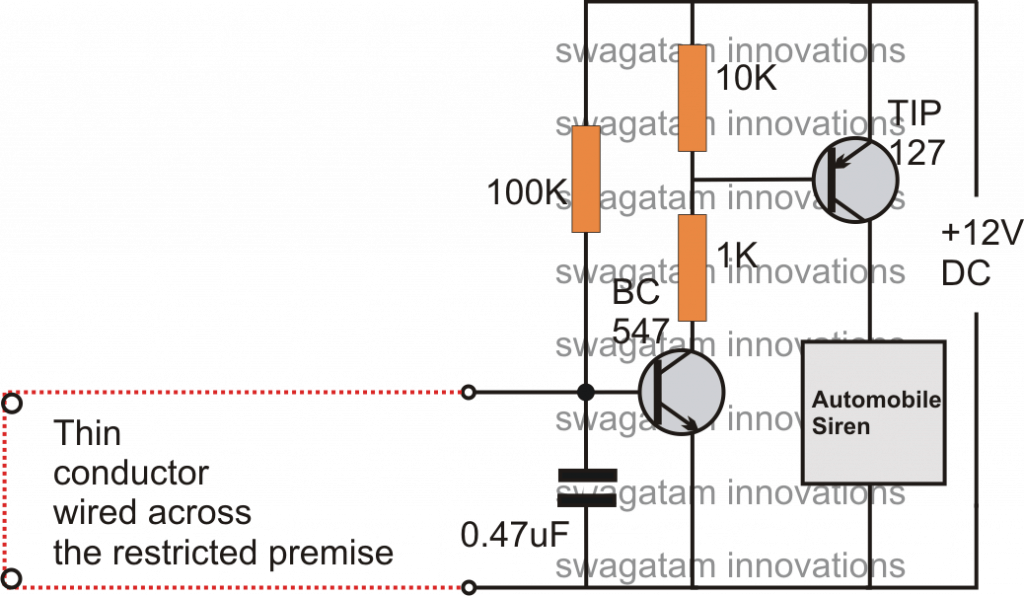

- Sistem Makluman Keselamatan berdasarkan PIC untuk Pelaksanaan FPGA dengan Spartan 3an

- Pelaksanaan FPGA untuk Merancang Pengawal untuk Sistem Sensor Jauh

- Kit Pemprosesan Imej FPGA menggunakan Penapisan Imej Linear & Morfologi

- Pelaksanaan Imej Fusion Perubatan berasaskan Spartan3 FPGA

Senarai Projek mini VLSI menggunakan kod VHDL merangkumi perkara berikut.

- Perbandingan dengan Kelajuan Tinggi menggunakan VLSI

- Pengganda Floating-Point menggunakan VLSI

- Penukaran berdasarkan Binari ke Kelabu berdasarkan VLSI

- Penapis Digital

- CLK Gating berdasarkan VLSI

- Pengganda Veda

- CMOS FF menggunakan VLSI

- Senibina Parallel Processor menggunakan VLSI

- Penambah Penuh berasaskan VLSI

- Reka bentuk DRAM / Memori Akses Rawak Dinamik berdasarkan VLSI

- Susun atur SRAM berdasarkan VLSI

- Pemproses Isyarat Digital berasaskan VLSI

- Multiplexer berasaskan VLSI

- Perancangan Unit MAC berdasarkan VLSI

- Pembezaan berasaskan VLSI

- FFT berasaskan VLSI atau Fast Fourier Transform

- Senibina Discrete Cosine Transform berdasarkan VLSI

- Reka Bentuk Pengganda 16-bit menggunakan VLSI19

- Perancangan berasaskan VLSI Buffer FIFO

- Pemecut Berkelajuan Tinggi berdasarkan VLSI

Projek VLSI menggunakan MATLAB & Xilinx

Senarai projek VLSI berdasarkan MATLAB dan Projek VLSI menggunakan Xilinx merangkumi yang berikut.

- Reka Bentuk & Analisis Modem CDMA dengan MATLAB

- Reka Bentuk Penapis FIR menggunakan VHDL pada Analisis berdasarkan FPGA & MATLAB

- Model Sim & Matlab atau Simulink berdasarkan Simulasi Sistem untuk Kejuruteraan Automotif

- Penambah berasaskan Xilinx seperti Ripple Carry & Carry Skip

- Unit Aritmetik berdasarkan Titik Terapung 32-bit

- ALU berasaskan Titik Terapung

- Pemproses RISC berdasarkan 32-bit

- Keupayaan Konvolusi Kod Orthogonal

- Mesin layan diri berasaskan Xilinx dan Verilog

- Penambah Awalan Paralel berasaskan Xilinx dengan 256-bit

- Protokol untuk Pengesahan Bersama menggunakan Xilinx

- Struktur Akses dengan Kitaran Tunggal untuk Uji Logik menggunakan Xilinx

- UTMI & Protocol Layer berasaskan USB2.0 menggunakan Xilinx

- Konfigurasi Pemampatan Data dan Penyahmampatan menggunakan Xilinx FPGA

- FPGA berasaskan BIST & Spartan Series Xilinx 4000

- Penapis IIR berdasarkan MATLAB & VLSI

- Penapis FIR menggunakan MATLAB

Projek IEEE

The senarai Projek IEEE VLSI disenaraikan di bawah.

- Sistem Automasi Rumah Tanpa Wayar berasaskan VLSI menggunakan Bluetooth

- Menghilangkan Kebisingan Impuls dalam Gambar dengan menggunakan Senibina Efisien VLSI

- Senibina Pemproses Dalam Memori untuk Mampatan Multimedia

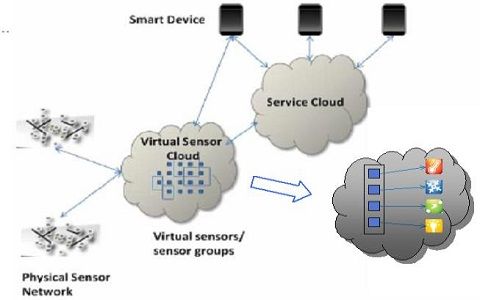

- Pemantauan Sistem Suhu menggunakan Cloud & IoT

- Pelaksanaan Sistem OFDM dengan IFFT & FFT

- Reka Bentuk & Pelaksanaan Kod Hamming dengan Verilog

- Pengenalan Cetakan Jari berasaskan VHDL menggunakan Gabor Filter

- Pemetaan Fungsi Aritmetik dengan ROM Bergantung pada Pendekatan Pendekatan

- Analisis Prestasi Kecekapan Tinggi & Ketumpatan Rendah Pengekod Kod Parity-Check dalam Aplikasi Berkekuatan Rendah

- Senibina FFT dengan Feedforward of Pipelined Radix-2k

- Flip-Flops Design untuk Aplikasi VLSI menggunakan Teknologi CMOS dengan Prestasi Tinggi

- Reka Bentuk Penapis FIR dengan Jadual Pencarian mengikut Aritmetik Teragih

- Pemproses Skala Imej Kos Rendah & Peningkatan berdasarkan VLSI

- Pelaksanaan ASIC & Reka bentuk Pengekodan & Penyahkod Turbo Advance dengan 3GPP LTE

- Patch-Pulled Patched Latches dengan Kuasa Rendah & Berkelajuan Tinggi Bersyarat

- Imbasan yang Disempurnakan dalam Ujian Imbasan Daya Rendah

- Aritmetik Coder VLSI Architecture untuk SPIHT

- Pelaksanaan VHDL untuk UART

- Pengatur Voltan berasaskan VLSI dengan Penurunan Rendah

- Reka Bentuk Flash ADC dengan Skim Perbandingan yang Disempurnakan

- Reka Bentuk Pengganda Daya Rendah dengan Gaya Logik Kelewatan Konstan Senyawa

- Double Tail Comparator dengan Prestasi Tinggi & Daya Rendah

- Sistem Penyimpanan Kilat dengan Prestasi Tinggi bergantung pada Tulis Penyangga & Memori Maya

- FF Daya Rendah berdasarkan Pendekatan Sleepy Stack

- Pengoptimuman Daya LFSR untuk BIST berkuasa rendah Dilaksanakan dalam HDL

- Reka Bentuk & Pelaksanaan Mesin Layan Diri dengan Verilog HDL

- Reka Bentuk Akumulator berdasarkan Penjanaan Corak 3-Berat dengan LP-LSFR

- Dekoder Reed-Solomon dengan Kelajuan Tinggi & Kerumitan Rendah

- Teknik Reka Bentuk Pengganda Dadda Lebih Cepat

- Penerima Radio FM berasaskan Demodulasi Digital

- Penjanaan Corak Ujian dengan Skema BIST

- Pelaksanaan Senibina VLSI dengan Paip Berkelajuan Tinggi

- Reka Bentuk Protokol OCP On-Chip Bus menggunakan Fungsi Bas

- Reka Bentuk Pengesan Frekuensi Fasa & Pam Pengecas yang digunakan untuk Gelung Berkunci Fasa Frekuensi Tinggi

- Cache Memory & Cache Controller Design dengan VHDL

- ASTRAN Pelaksanaan Pemampat Adder Daya Rendah 3-2 & 4-2

- Sistem Bil Elektrik Prabayar menggunakan Reka Bentuk On-Chip

- Pelaksanaan Bertindih menggunakan sel Logik & Analisis Kuasanya

- Carry Look Ahead Adder dengan Analisis Prestasi Bit yang berbeza menggunakan VHDL

- Reka Bentuk Lapisan Pautan Data dengan Wi-Fi MAC Protokol

- Pelaksanaan FPGA untuk Protokol Pengesahan Bersama dengan Aritmetik Modular

- Penjanaan Isyarat PWM menggunakan FPGA & Variable Duty Cycle

Projek Masa Nyata

Senarai Projek masa nyata VLSI terutamanya merangkumi projek mini VLSI menggunakan kod VHDL dan projek perisian VLSI untuk pelajar kejuruteraan ECE.

- Integrasi Pragmatik SRAM Row Cache dalam Senibina DRAM 3-D Heterogen Menggunakan TSV

- Teknik Uji Diri Built-In untuk Diagnosis Kesalahan Kelewatan dalam Aras Gerbang Berprogram Bidang Berasaskan Kluster

- Reka Bentuk ASIC Pengganda Kompleks

- Pelaksanaan VLSI Kos Rendah untuk Penghapusan Kebisingan Impuls yang Efisien

- Berasaskan FPGA Vektor Ruang PWM Control IC Untuk Pemacu Motor Induksi Tiga Fasa

- Pelaksanaan VLSI Auto Correlator dan CORDIC Algorithm for OFDM Based WLAN

- Pengekstrakan Jalan Automatik Menggunakan Imej Satelit Resolusi Tinggi

- Reka Bentuk VHDL untuk Segmentasi Imej Menggunakan Penapis Gabor untuk Pengesanan Penyakit

- Senibina Turbo Decoder Kerumitan Rendah untuk Rangkaian Sensor Tanpa Wayar Berkekuatan Tenaga

- Peningkatan Keupayaan Konvolusi Kod Orthogonal Menggunakan Pelaksanaan FPGA

- Reka Bentuk dan Pelaksanaan ALU Titik Terapung

- Reka bentuk CORDIC untuk Sudut Putaran Tetap

- Produk Reed-Solomon Code untuk Menerapkan NAND Flash Controller pada FPGA Chip

- Peningkatan Hasil Akses SRAM Statistik Menggunakan Litar Kapasitansi Negatif

- Pengurusan Kuasa Antara Muka Rangkaian MIMO pada Sistem Mudah Alih

- Reka Bentuk Piawai Penyulitan Data untuk Penyulitan Data

- Daya Rendah dan Kawasan Berkekalan Pilih Adder

- Sintesis dan Pelaksanaan UART Menggunakan Kod VHDL

- Senibina yang Ditingkatkan untuk Unit Penambahan Titik Terapung Fused

- Pemancar Semua-Digital 1-Bit Berasaskan FPGA yang Menggunakan Modulasi Delta-Sigma dengan Output RF untuk SDR

- Mengoptimumkan Penggunaan Pencarian Rantai dalam Decoder BCH untuk Penghantaran Kadar Ralat Tinggi

- Reka Bentuk Digital Pemancar DS-CDMA Menggunakan Verilog HDL dan FPGA

- Reka Bentuk dan Pelaksanaan Senibina Array Sistolik yang Efisien

- Algoritma Pembelajaran Dinamika Robot Berasaskan VLSI

- Reka Bentuk Unit Fungsi Multimedia Serbaguna Menggunakan Teknik Penekanan Kuasa Spurious

- Reka bentuk Jambatan Bas antara AHB dan OCP

- Tingkah Laku Sintesis Litar Asinkron

- Pengoptimuman Kelajuan Decoder Viterbi Modifikasi Berasaskan FPGA

- Pelaksanaan Antaramuka I2C

- Pengganda Berkelajuan Tinggi / Daya Rendah Menggunakan Teknik Penekanan Kuasa Lumayan Lanjutan

- Mengapit Voltan Bekalan Maya Litar Power Gated untuk Pengurangan Kebocoran Aktif dan Kebolehpercayaan Oksida Gerbang

- Channelizer Cekap Kuasa Berasaskan FPGA untuk Radio yang Ditetapkan Perisian

- Arkitek VLSI dan Prototaip FPGA Kamera Digital untuk Keselamatan dan Pengesahan Imej

- Operasi Penambahbaikan Robot Dalaman

- Reka Bentuk dan Pelaksanaan Rangkaian Permutasi ON-Chip untuk Sistem Multiprocessor-On-Chip

- Kaedah Penyegerakan Waktu Laju Simbol untuk Sistem OFDM Tanpa Wayar Daya Rendah

- Pengawal DMA (Akses Memori Langsung) Menggunakan VHDL / VLSI

- FFT yang boleh dikonfigurasi semula menggunakan seni bina berasaskan CORDIC untuk Penerima MIMI-OFDM

- Teknik Penindasan Kuasa Spurious untuk Aplikasi Multimedia / DSP

- Kecekapan Kod BCH dalam Tanda Air Gambar Digital

- Pengawal SD-RAM Kadar Data Ganda

- Melaksanakan Gabor Filter untuk Pengecaman Cap Jari Menggunakan Verilog HDL

- Reka Bentuk Skala Nanometer Praktikal yang berlebihan melalui Perpustakaan Sel Standard Aware untuk Peningkatan yang berlebihan melalui 1 Kadar Penyisipan

- Algoritma Pemampatan Data dan Penyahmampatan dan Senibina Perkakasannya

- Rangka Kerja untuk Pembetulan Kesalahan Lembut Berbilang Bit

- Pemampatan Data Ujian Efisien Berasaskan Viterbi

- Pelaksanaan Blok FFT / IFFT untuk OFDM

- Pemampatan Imej Berasaskan Wavelet oleh VLSI Progressive Coding

- Pelaksanaan VLSI Pengganda Berpelaburan Sepenuhnya Tolak Senibina DCD / IDCT 2d untuk Jpeg

- Emulasi Kesalahan Berasaskan FPGA Litar Berurutan Segerak

Oleh itu, ini adalah mengenai senarai projek VLSI untuk kejuruteraan, pelajar M.Tech yang sangat membantu dalam memilih topik projek tahun akhir mereka. Setelah menghabiskan masa berharga anda ketika melalui senarai ini, kami percaya bahawa anda mempunyai idea yang cukup baik untuk memilih topik projek pilihan anda dari senarai projek VLSI, dan berharap anda mempunyai keyakinan yang cukup untuk mengambil topik dari senarai. Untuk keterangan lebih lanjut dan bantuan mengenai projek-projek ini, anda boleh menulis kepada kami di bahagian komen yang diberikan di bawah. Inilah soalan untuk anda, apa itu VHDL?

Kredit Foto

- Projek VLSI oleh set-teknologi