Kami tahu bahawa dalam semua elektrikal dan litar elektronik , kapasitor mempunyai kepentingan yang unik. Kesan sedemikian kapasitor dapat dianalisis dengan tindak balas frekuensi. Ini bermaksud kesan kapasitansi pada frekuensi yang lebih rendah dan lebih tinggi dan reaktansinya dapat dianalisis dengan mudah dengan tindak balas frekuensi. Di sini kita membincangkan istilah penting yang disebut kesan penggiling dalam penguat , dan definisi dan kesan kapasitansi miller.

Apakah Kesan Miller?

Nama kesan miller diambil dari karya John Milton miller. Dengan bantuan teorema miller, kapasitansi litar setara penguat voltan terbalik dapat ditingkatkan dengan meletakkan impedans tambahan antara terminal input dan output litar. Teorema Miller menyatakan bahawa litar mempunyai impedans (Z), menghubungkan antara dua nod di mana tahap voltan adalah V1 dan V2.

Apabila impedans ini digantikan oleh dua nilai impedans yang berbeza dan disambungkan ke terminal input & output yang sama ke tanah untuk menganalisis tindak balas frekuensi penguat serta untuk meningkatkan kapasitansi input. Kesan sedemikian disebut kesan Miller. Kesan ini hanya berlaku di pembalik terbalik .

Kesan Kapasiti Miller

Kesan ini melindungi kapasiti litar setara. Pada frekuensi yang lebih tinggi, kenaikan litar dapat dikendalikan atau dikurangkan oleh kapasitansi pengisar kerana menangani penguat voltan terbalik pada frekuensi tersebut adalah proses yang kompleks.

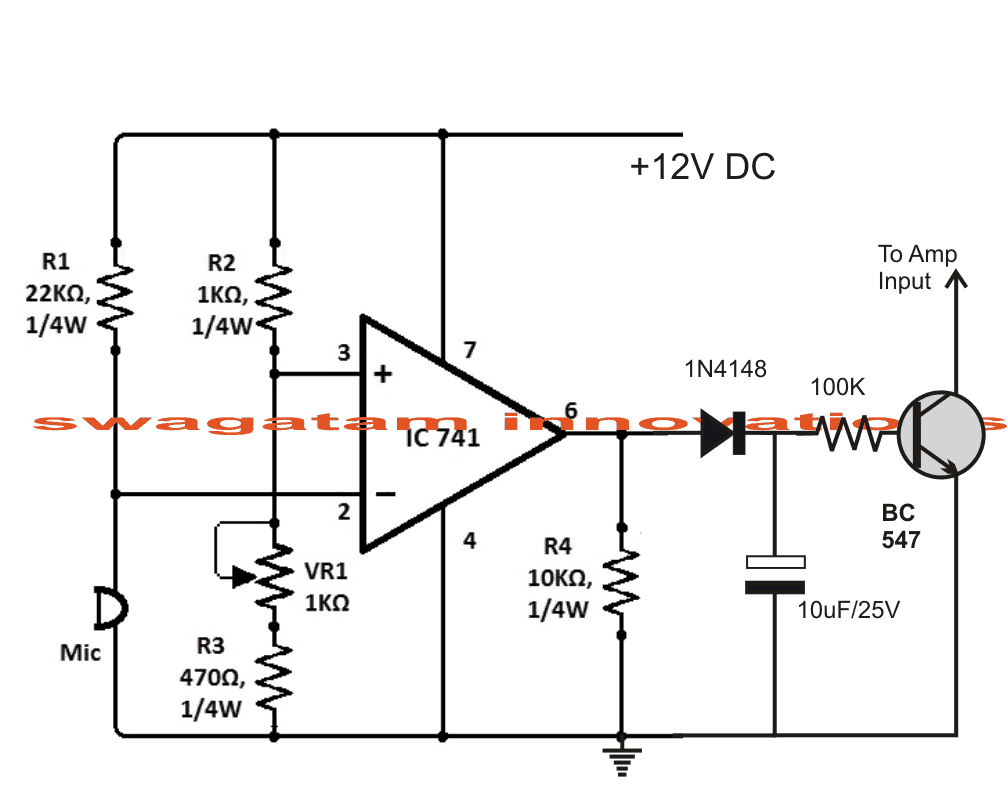

pengilang pertama

Sekiranya terdapat beberapa kapasitansi antara input & output dari penguat voltan terbalik maka ia akan kelihatan dikalikan dengan keuntungan penguat. Jumlah kapasitansi tambahan akan disebabkan oleh kesan ini sehingga dinamakan Miller capacitance.

pengilang kedua

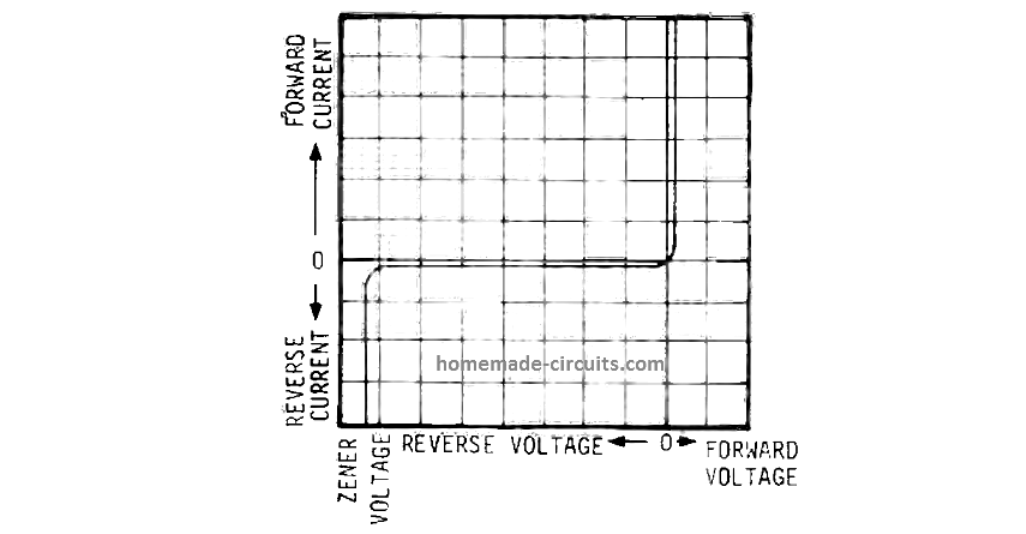

Rajah di bawah menunjukkan penguat voltan terbalik yang ideal dan Vin adalah voltan masukan dan Vo adalah voltan keluaran, Z adalah impedans, keuntungan ditunjukkan oleh –Av. Dan voltan keluaran Vo = -Av.Vi

penguat voltan-voltan-ideal

Di sini, penguat voltan terbalik yang ideal menarik arus sifar dan semua arus mengalir melalui impedans Z.

Kemudian, semasa I = Vi-Vo / Z

I = Vi (1 + Av) / Z

Impedans input Zin = Vi / Ii = Z / 1 + Av .

Sekiranya Z mewakili kapasitor dengan impedans, maka Z = 1 / sC.

Oleh itu input impedans Kalimat = 1 / sCm

Di sini Cm = C (1 + Av)

Kapasiti Cm-miller.

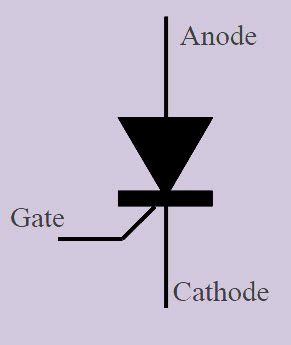

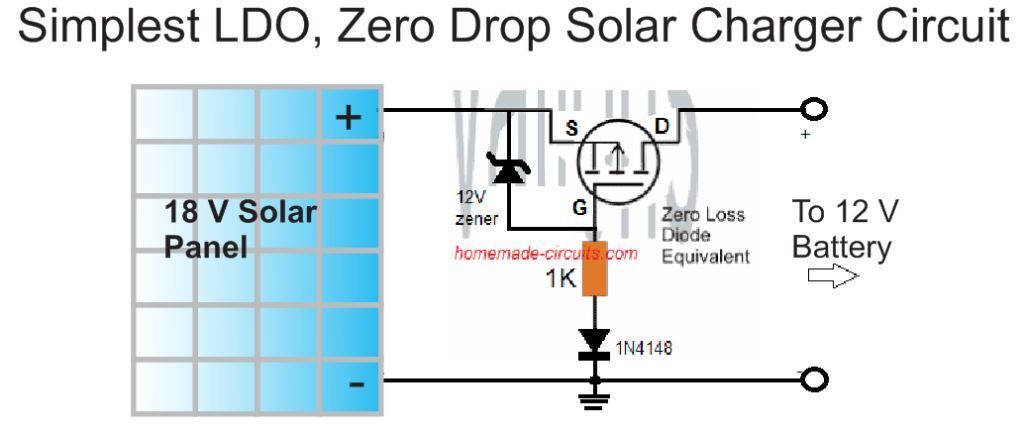

Kesan Miller dalam IGBT

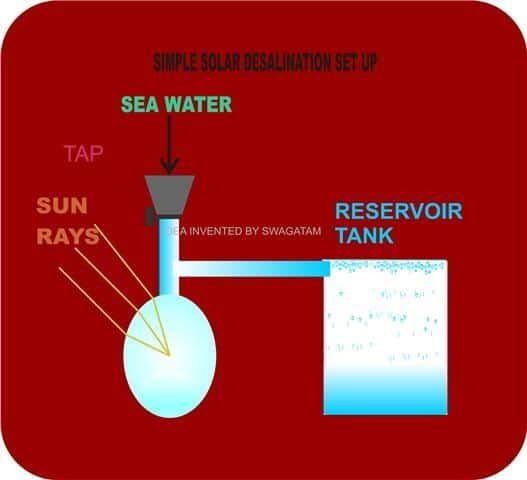

Di dalam IGBT (transistor bipolar pintu bertebat) , kesan ini akan berlaku kerana strukturnya. Dalam litar setara IGBT di bawah, dua kapasitor dalam bentuk siri.

miller-effect-in-IGBT

Nilai kapasitor pertama tetap dan nilai kapasitor kedua bergantung pada lebar kawasan drift & voltan pemungut-pemancar. Jadi, apa-apa perubahan dalam Vce yang menyebabkan arus anjakan melalui kapasitansi miller. Pangkalan biasa & penguat pemungut biasa tidak akan merasakan kesan pengisar. Kerana dalam penguat ini, satu sisi kapasitor (Cu) disambungkan ke tanah. Ini membantu mengeluarkannya dari kesan pengisar.

Oleh itu, kesan ini digunakan terutamanya untuk meningkatkan kapasitansi litar dengan meletakkan impedans antara nod input dan output litar. Kemudian kapasitans tambahan diperlakukan sebagai kapasitansi miller. Teorema Miller berlaku untuk semua peranti tiga terminal. Di FET juga pintu untuk mengalirkan kapasitansi dapat ditingkatkan dengan kesan ini. Tetapi ia boleh menjadi masalah dalam rangkaian jalur lebar. Apabila kapasitansi meningkat lebar jalur akan dikurangkan. Dan dalam litar jalur sempit, kesan pengisar sedikit kurang. Ini perlu diperbaiki dengan beberapa pengubahsuaian.