Dalam catatan ini kita membincangkan penilaian avalanche MOSFET, dan belajar bagaimana memahami penilaian ini dalam lembar data dengan betul, bagaimana parameter diuji oleh pengeluar, dan langkah-langkah untuk melindungi MOSFET dari fenomena ini.

Parameter longsoran tidak hanya membantu mengesahkan kekasaran peranti, ia juga membantu menyaring MOSFET yang lebih lemah atau yang lebih rentan atau berisiko mengalami kerosakan.

Apa itu MOSFET Avalanche Rating

Peringkat avalanche MOSFET adalah tenaga maksimum yang boleh ditoleransi (milijoule) yang dapat ditahan oleh MOSFET, apabila voltan sumber salirannya melebihi had voltan kerosakan maksimum (BVDSS).

Fenomena ini biasanya berlaku pada litar pensuisan MOSFET dengan beban induktif melintasi terminal saliran.

Semasa tempoh ON dari kitaran pensuisan, induktor mengenakan cas, dan selama masa OFF induktor melepaskan tenaga tersimpannya dalam bentuk EMF belakang merentasi sumber longkang MOSFET.

Voltan terbalik ini melalui dioda badan MOSFET, dan jika nilainya melebihi had maksimum yang boleh ditoleransi pada peranti, menyebabkan panas yang kuat berkembang di dalam peranti yang menyebabkan bahaya atau kerosakan kekal pada peranti.

Bilakah MOSFET Avalanche Diperkenalkan

Parameter Avalanche Energy dan UIS (peralihan induktif yang tidak ditutup) sebenarnya tidak termasuk dalam lembaran data MOSFET sebelum tahun 1980-an.

Dan ketika itulah ia berkembang menjadi bukan hanya spesifikasi lembar data, tetapi parameter yang mana banyak pengguna mulai menuntut agar FET diuji sebelum melewati perangkat untuk produksi, terutama jika MOSFET sedang dirancang untuk bekalan kuasa atau beralih pelaksanaan.

Oleh itu, hanya setelah tahun 1980-an parameter longsoran mula muncul di lembar data, dan kemudian juruteknik promosi mula memahami bahawa semakin besar penilaian longsoran, semakin kompetitif perangkat tersebut.

Para jurutera mula menentukan teknik untuk bereksperimen dengan parameter dengan mengubah beberapa pemboleh ubahnya, yang digunakan untuk proses pengujian.

Secara amnya, semakin besar tenaga longsor, semakin kuat dan kuat MOSFET berubah menjadi. Oleh itu, penilaian longsoran yang lebih besar, mewakili ciri-ciri MOSFET yang lebih kuat.

Sebilangan besar lembar data FET biasanya mempunyai parameter longsoran yang termasuk dalam Jadual Penilaian Maksimum Mutlak mereka, yang dapat ditemukan secara langsung di halaman entri lembaran data. Terutama, anda dapat melihat parameter di sini yang ditulis sebagai Avalanche Current dan Avalanche Energy, Eas.

Oleh itu, dalam lembaran data MOSFET Avalanche Energy disajikan sebagai kuantiti tenaga yang dapat ditoleransi oleh MOSFET ketika sedang menjalani ujian longsoran, atau ketika peringkat voltan kerosakan maksimum MOSFET dilintasi.

Avalanche Semasa dan UIS

Peringkat voltan pemecahan maksimum ini ditentukan melalui Avalanche Current Test, yang dicapai melalui ujian Unclamped Inductive Switching atau ujian UIS.

Oleh itu, semasa jurutera membincangkan mengenai arus UIS, mereka mungkin merujuk kepada Arus Avalanche.

Ujian Pengalihan Induktif Tidak Dikendalikan dilakukan untuk mengetahui arus dan dengan itu tenaga longsor yang boleh mencetuskan kegagalan MOSFET.

Seperti yang telah disebutkan sebelumnya, besar atau penarafan ini sangat bergantung pada spesifikasi ujian, terutamanya, nilai induktor yang diterapkan pada saat ujian.

Persediaan Ujian

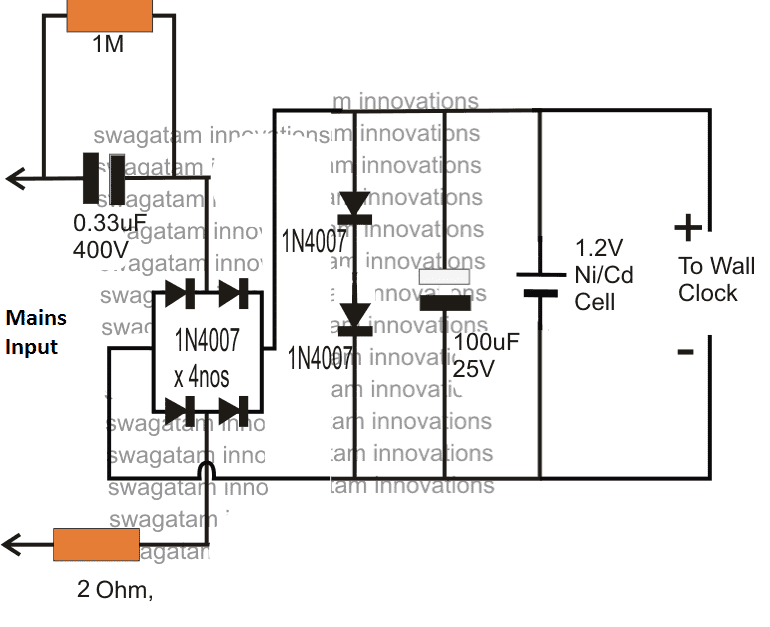

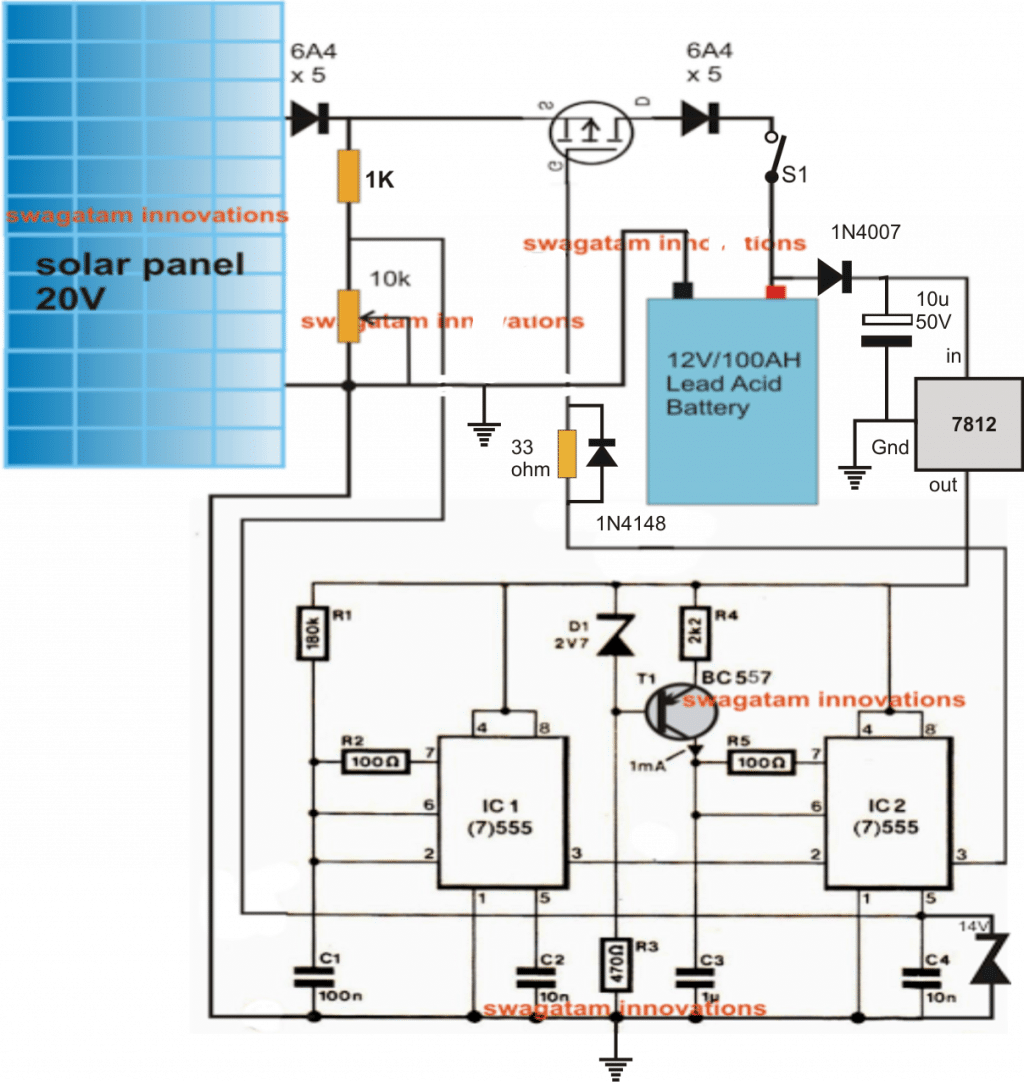

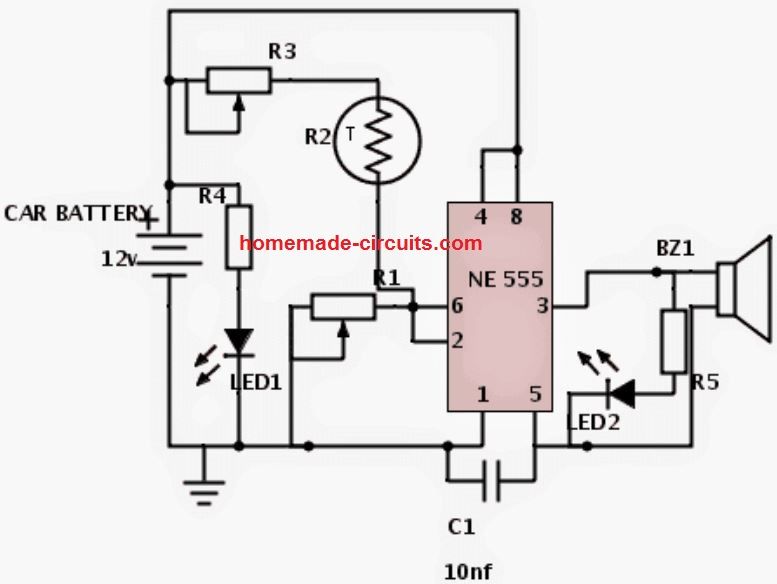

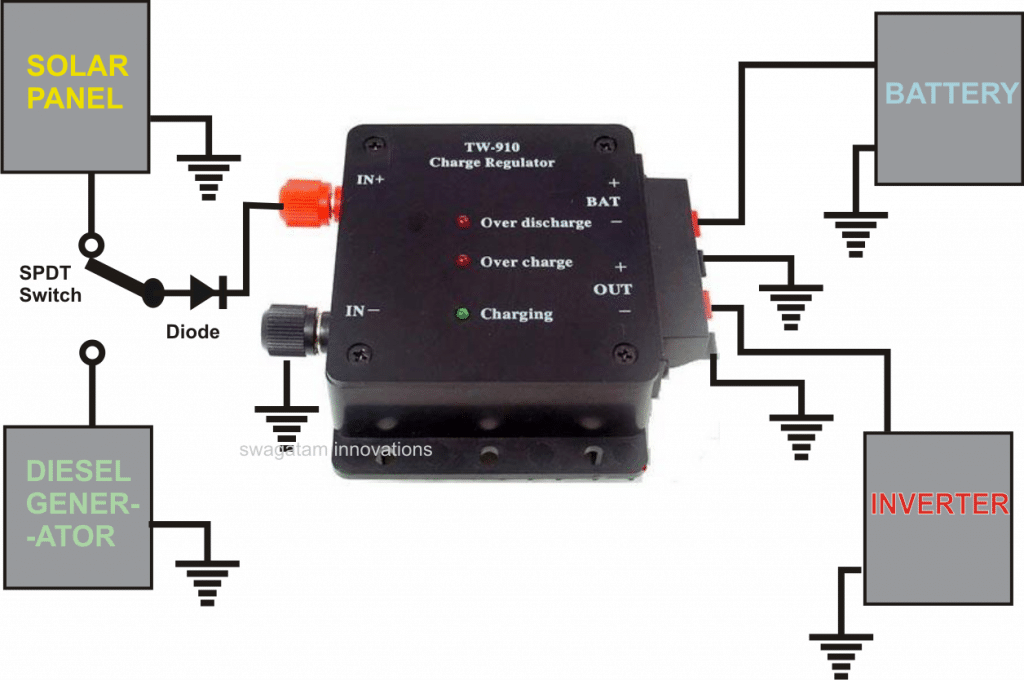

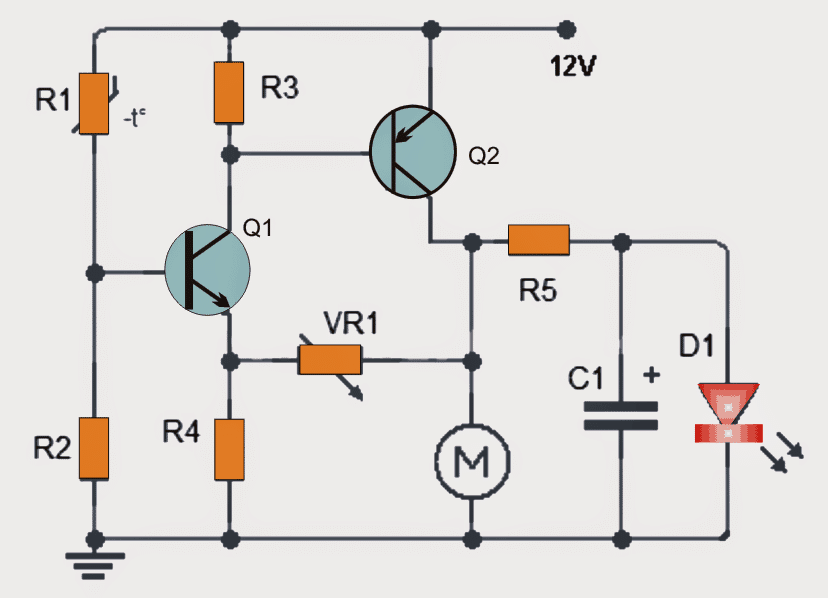

Gambar rajah berikut menunjukkan susunan litar ujian UIS standard.

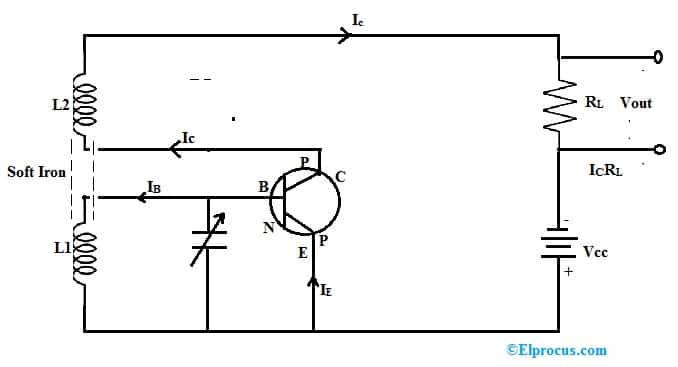

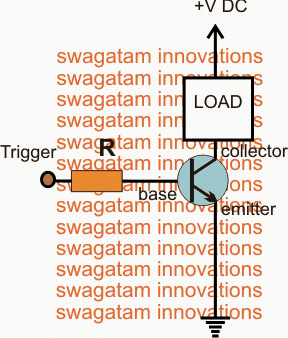

Oleh itu, kita melihat bekalan voltan secara bersiri dengan induktor, L, yang juga bersiri dengan MOSFET yang diuji. Kita juga dapat melihat pemacu gerbang untuk FET yang outputnya bersiri dengan perintang gerbang FET R.

Dalam gambar di bawah, kita dapati, alat pengawal LTC55140, yang digunakan di makmal Texas Instrument untuk menilai ciri-ciri UIS dari FET.

Karakteristik UIS kemudiannya membantu bukan sahaja untuk mengetahui peringkat lembar data FET, tetapi juga nilai yang digunakan untuk mengimbas FET dalam prosedur ujian akhir.

Alat ini membolehkan mengubah nilai induktor beban dari 0.2 hingga 160 miliheneri. Ia membolehkan penyesuaian voltan saliran MOSFET yang diuji dari 10 hingga 150 volt.

Ini, sebagai hasilnya memungkinkan untuk menyaring bahkan FET yang dinilai hanya menangani voltan kerosakan 100 volt. Dan, mungkin berlaku pengaliran arus dari 0.1 hingga 200 amp. Dan ini adalah jarak semasa UIS yang mungkin harus ditoleransi oleh FET semasa prosedur ujian.

Selain itu alat ini membolehkan menetapkan julat suhu kes MOSFET yang berbeza, dari -55 hingga +150 darjah.

Prosedur Ujian

UIS standard UIS dilaksanakan melalui 4 tahap, seperti yang digambarkan dalam gambar berikut:

Tahap pertama terdiri daripada ujian pra-kebocoran, di mana voltan bekalan memalirkan aliran FET. Pada dasarnya, idea di sini adalah untuk berusaha memastikan FET berkinerja seperti yang diharapkan.

Oleh itu, pada peringkat pertama FET diadakan dimatikan. Ia memastikan voltan bekalan tersekat di terminal daim-emitter, tanpa mengalami arus kebocoran berlebihan yang mengalir melaluinya.

Pada tahap kedua, yang dikenal sebagai jalan arus Avalanche, FET dihidupkan, yang menyebabkan voltan salirannya turun. Ini mengakibatkan arus meningkat secara beransur-ansur melalui induktor dengan di / dt tetap. Jadi pada dasarnya pada tahap ini, induktor dibenarkan untuk mengisi.

Pada tahap ketiga, ujian longsoran longsor dilakukan, di mana FET secara praktikal mengalami longsoran longsor. Pada tahap ini FET dimatikan dengan menghapus bias gerbangnya. Ini mengakibatkan di / dt besar-besaran melalui induktor, menyebabkan voltan saliran FET menembak tinggi di atas had voltan kerosakan FET.

Ini memaksa FET menjalani lonjakan longsoran. Dalam proses ini, FET menyerap keseluruhan tenaga yang dihasilkan oleh induktor, dan tetap dimatikan, sehingga tahap ke-4 dilaksanakan, yang melibatkan ujian pasca kebocoran

Pada tahap ke-4 ini, FET sekali lagi menjalani ujian longsoran berulang, untuk memastikan sama ada MOSFET masih berkelakuan normal atau tidak. Sekiranya berjaya, maka FET dianggap telah lulus ujian longsoran.

Seterusnya, FET harus melalui ujian di atas berkali-kali, di mana tahap voltan UIS secara beransur-ansur meningkat dengan setiap ujian, sehingga tahap di mana MOSFET tidak dapat bertahan dan gagal dalam ujian pasca kebocoran. Dan tahap semasa ini dinyatakan sebagai keupayaan tahan maksimum MISFET UIS semasa.

Mengira Tenaga Avalanche MOSFET

Setelah kapasiti pengendalian maksimum MISFET UIS dapat dicapai, di mana peranti rosak, menjadi lebih mudah bagi jurutera untuk menganggar kuantiti tenaga yang dikeluarkan melalui FET semasa proses longsoran.

Dengan andaian, seluruh tenaga yang tersimpan di induktor telah disalurkan ke dalam MOSFET semasa longsoran, besarnya tenaga ini dapat ditentukan dengan menggunakan formula berikut:

ADALAHSEBAGAI= 1 / 2L x IDARIdua

ADALAHSEBAGAImemberi kita besarnya tenaga yang tersimpan di dalam induktor, yang sama dengan 50% dari nilai induktansi dikalikan dengan kuasa dua arus, mengalir melalui induktor.

Selanjutnya, diperhatikan bahawa ketika nilai induktor meningkat, jumlah arus yang bertanggungjawab untuk pemecahan MOSFET benar-benar menurun.

Walau bagaimanapun, peningkatan ukuran induktor ini sebenarnya mengimbangi pengurangan arus dalam formula tenaga di atas dengan cara bahawa nilai tenaga meningkat secara harfiah.

Tenaga Avalanche atau Avalanche Semasa?

Ini adalah dua parameter, yang dapat membingungkan pengguna, sambil memeriksa lembar data MOSFET untuk penilaian longsoran.

Hak Cipta © Texas Instruments Incorporated

Sebilangan besar pengeluar MOSFET sengaja menguji MOSFET dengan induktor yang lebih besar, sehingga mereka dapat membanggakan kekuatan tenaga longsor yang lebih besar, mewujudkan kesan bahawa MOSFET diuji untuk menahan tenaga longsoran besar, dan oleh itu mempunyai daya tahan yang meningkat untuk longsoran.

Tetapi kaedah menggunakan induktor yang lebih besar di atas nampaknya mengelirukan, itulah sebabnya mengapa jurutera Texas Instruments menguji dengan induktansi yang lebih kecil dalam urutan 0.1 mH, sehingga MOSFET yang diuji mengalami tahap tekanan semasa Avalanche yang lebih tinggi dan kerosakan yang teruk.

Jadi, dalam lembaran data, bukan tenaga Avalanche, sebaliknya arus Avalanche yang seharusnya lebih besar dari segi kuantitas, yang menunjukkan kekasaran MOSFET yang lebih baik.

Ini menjadikan ujian akhir sangat ketat dan membolehkan menyaring sebanyak mungkin MOSFET yang lebih lemah.

Nilai ujian ini tidak hanya digunakan sebagai nilai akhir sebelum tata letak FET diteruskan untuk produksi, tetapi ini juga nilai yang dimasukkan dalam lembar data.

Pada langkah seterusnya, nilai ujian di atas diturunkan sebanyak 65%, sehingga pengguna akhir dapat memperoleh margin toleransi yang lebih luas untuk MOSFET mereka.

Jadi, sebagai contoh, jika arus longsor yang diuji adalah 125 Amps, nilai akhir yang dimasukkan dalam lembar data adalah 81 Amps, setelah ditolak.

MOSFET Avalanche Semasa vs Masa yang dihabiskan di Avalanche

Parameter lain yang dikaitkan dengan kekuatan MOSFET dan disebut dalam lembar data, terutama untuk MOSFET yang dirancang untuk menukar aplikasi adalah Avalanche Current Capability berbanding Time Spent di Avalanche. Parameter ini biasanya ditunjukkan berkenaan dengan suhu kes MOSFET pada 25 darjah. Semasa ujian suhu kes meningkat kepada 125 darjah.

Dalam keadaan ini suhu kes MOSFET MOSFET hampir hampir dengan suhu persimpangan sebenar silikon MOSFET.

Dalam prosedur ini apabila suhu persimpangan peranti meningkat, anda mungkin akan melihat penurunan yang agak normal? Walau bagaimanapun, jika hasilnya menunjukkan tahap penurunan yang tinggi, itu mungkin menunjukkan tanda-tanda peranti MOSFET yang lemah.

Oleh itu dari sudut pandangan reka bentuk, usaha dilakukan untuk memastikan bahawa penurunan tidak melebihi 30% untuk kenaikan suhu kes dari 25 hingga 125 darjah.

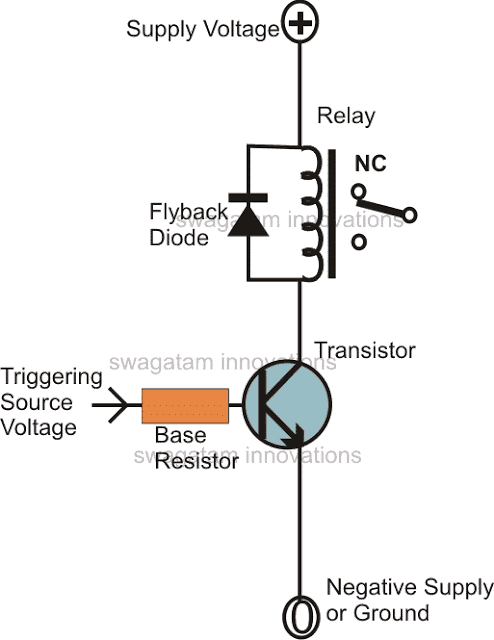

Cara Melindungi MOSFET dari Avalanche Current

Seperti yang kita ketahui dari perbincangan di atas, longsoran di MOSFET dikembangkan kerana EMF belakang induktif voltan tinggi beralih melalui diod badan MOSFET.

Sekiranya voltan EMF belakang ini melebihi penarafan maksimum diod badan, menyebabkan penjanaan haba yang melampau dalam peranti dan kerosakan seterusnya.

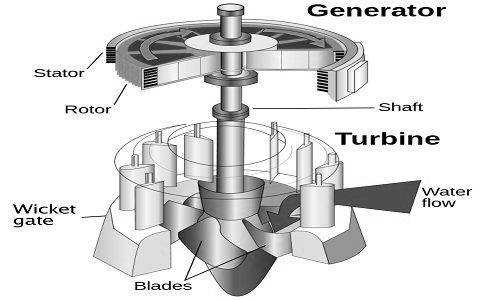

Ini menunjukkan bahawa jika voltan EMF induktif dibiarkan melewati diod pintas luaran yang sesuai, melintasi saluran pemancar FET dapat membantu mengelakkan fenomena longsoran.

Gambar rajah berikut menunjukkan reka bentuk standard penambahan diod pemancar saluran luaran untuk menguatkan diod badan dalaman MOSFET.

Dengan hormat: Avalanche MOSFET

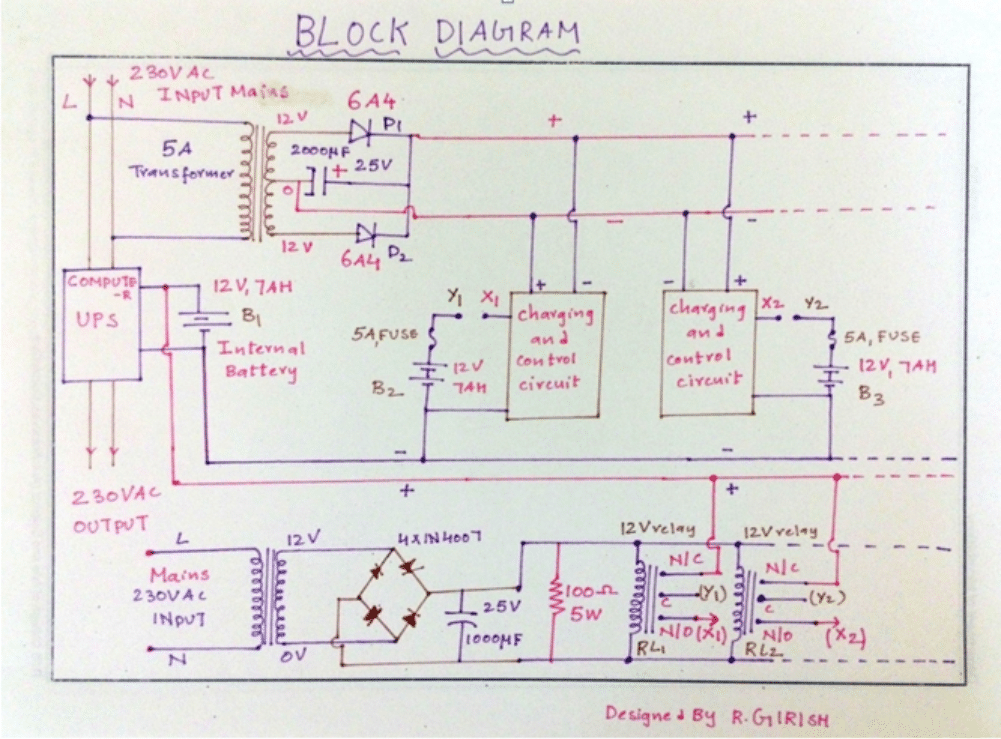

Sebelumnya: Menukarkan Pencucuhan Spark Yang Dibuang ke Spark Berurutan, untuk Pembakaran Berkecekapan Tinggi Seterusnya: Litar UPS Dalam Talian Mudah