Transistor MOS ialah elemen paling asas dalam reka bentuk litar bersepadu berskala besar. Transistor ini biasanya dikelaskan kepada dua jenis PMOS dan NMOS. Gabungan transistor NMOS dan PMOS dikenali sebagai a transistor CMOS . Perbezaan gerbang logik & peranti logik digital lain yang dilaksanakan mesti mempunyai logik PMOS. Teknologi ini murah & mempunyai ketahanan yang baik terhadap gangguan. Artikel ini membincangkan salah satu jenis transistor MOS seperti transistor PMOS.

Apakah Transistor PMOS?

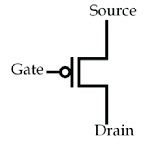

Transistor PMOS atau semikonduktor oksida logam P-channel ialah sejenis transistor di mana dopan jenis-p digunakan di kawasan saluran atau gerbang. Transistor ini betul-betul kebalikan Transistor NMOS. Transistor ini mempunyai tiga terminal utama; punca, get & longkang di mana sumber transistor direka bentuk dengan substrat jenis p, dan terminal longkang direka bentuk dengan substrat jenis-n. Dalam transistor ini, pembawa cas seperti lubang bertanggungjawab untuk pengaliran arus. Simbol transistor PMOS ditunjukkan di bawah.

Bagaimana Transistor PMOS Berfungsi?

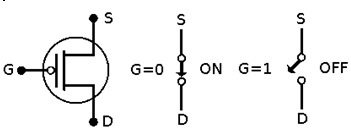

Transistor jenis-p berfungsi agak bertentangan dengan transistor jenis-n. Transistor ini akan membentuk litar terbuka apabila mendapat voltan tidak boleh diabaikan yang bermaksud, tiada pengaliran elektrik dari terminal get (G) ke punca (S). Begitu juga transistor ini membentuk litar tertutup apabila mendapat voltan sekitar 0 volt yang bermaksud arus mengalir dari terminal get (G) ke longkang (D).

Gelembung ini juga dikenali sebagai gelembung penyongsangan. Jadi fungsi utama bulatan ini adalah untuk menyongsangkan nilai voltan masukan. Jika terminal get memberikan voltan 1, maka penyongsang ini akan menukarnya kepada sifar dan berfungsi dengan litar dengan sewajarnya. Jadi fungsi transistor PMOS dan transistor NMOS agak bertentangan. Sebaik sahaja kita menggabungkannya ke dalam litar MOS tunggal, maka ia akan menjadi litar CMOS (complementary metal-oxide semiconductor).

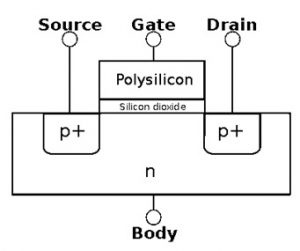

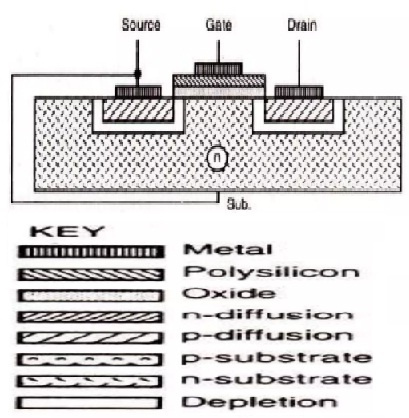

Keratan Rentas Transistor PMOS

Keratan rentas transistor PMOS ditunjukkan di bawah. Transistor pMOS dibina dengan badan jenis-n termasuk dua kawasan semikonduktor jenis-p yang bersebelahan dengan pintu masuk. Transistor ini mempunyai pintu kawalan seperti yang ditunjukkan dalam rajah yang mengawal aliran elektron antara dua terminal seperti punca & longkang. Dalam transistor pMOS, badan dipegang pada voltan +ve. Sebaik sahaja terminal pagar positif, maka terminal punca & longkang adalah bias songsang. Sebaik sahaja ini berlaku, tiada aliran arus, jadi transistor akan dimatikan.

Sebaik sahaja bekalan voltan di terminal get diturunkan, maka pembawa cas positif akan tertarik ke bahagian bawah antara muka Si-SiO2. Apabila voltan menjadi rendah dengan cukup maka saluran akan terbalik dan mewujudkan laluan pengalir dari terminal punca ke longkang dengan membenarkan pengaliran arus.

Setiap kali transistor ini berurusan dengan logik digital biasanya terdapat dua nilai yang berbeza sahaja seperti 1 & 0 (ON dan OFF). Voltan positif transistor dikenali sebagai VDD yang mewakili nilai logik tinggi (1) dalam litar digital. Tahap voltan VDD dalam Logik TTL biasanya sekitar 5V. Pada masa ini transistor sebenarnya tidak dapat menahan voltan tinggi sedemikian kerana ia biasanya berkisar antara 1.5V - 3.3V. Voltan rendah sering dikenali sebagai GND atau VSS. Jadi, VSS menandakan logik '0' dan ia juga ditetapkan secara normal kepada 0V.

Litar Transistor PMOS

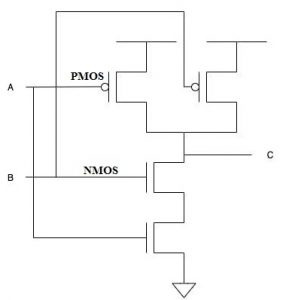

Reka bentuk get NAND menggunakan transistor PMOS dan transistor NMOS ditunjukkan di bawah. Secara amnya, get NAND dalam elektronik digital ialah get logik yang juga dipanggil get NOT-AND. Keluaran get ini adalah rendah (0) hanya jika dua input adalah tinggi (1) dan outputnya adalah pelengkap kepada get AND. Jika mana-mana dua input adalah RENDAH (0), maka ia memberikan hasil output yang tinggi.

Dalam litar logik di bawah, jika input A ialah 0 dan B ialah 0, maka A input pMOS akan menghasilkan '1' dan A input bagi nMOS akan menghasilkan '0'. Jadi, get logik ini menghasilkan logik ‘1’ kerana ia disambungkan kepada punca melalui litar tertutup & tertanggal daripada GND melalui litar terbuka.

Apabila A ialah '0' & B' ialah '1', maka input pMOS akan menghasilkan '1' & input NMOS akan menghasilkan '0'. Oleh itu, get ini akan menghasilkan satu logik kerana ia disambungkan kepada punca melalui litar tertutup dan tertanggal daripada GND oleh litar terbuka. Apabila A ialah '1' & B ialah '0', maka input 'B' pMOS akan menghasilkan output tinggi (1) & input 'B' NMOS akan menghasilkan output serendah (0). Jadi, get logik ini akan menghasilkan logik 1 kerana ia disambungkan kepada punca melalui litar tertutup & tertanggal daripada GND oleh litar terbuka.

Apabila A ialah '1' & B ialah '1', maka A input bagi' pMOS akan menghasilkan sifar, dan A input bagi nMOS akan menjana '1'. Akibatnya, kita harus mengesahkan input B pMOS & nMOS juga. Input B pMOS akan menjana '0' & input B nMOS akan menjana '1'. Jadi, get logik ini akan menjana logik ‘0’ kerana ia tertanggal daripada punca oleh litar terbuka & disambungkan kepada GND melalui litar tertutup.

Jadual Kebenaran

Jadual kebenaran litar logik di atas diberikan di bawah.

|

A |

B |

C |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

Voltan ambang Transistor PMOS biasanya adalah 'Vgs' yang diperlukan untuk mencipta saluran yang dikenali sebagai penyongsangan saluran. Dalam transistor PMOS, substrat & terminal sumber hanya disambungkan kepada 'Vdd'. Jika kita mula mengurangkan voltan dengan merujuk kepada terminal sumber di terminal get dari Vdd ke titik di mana sahaja anda melihat penyongsangan saluran, pada kedudukan ini jika anda menganalisis Vgs & sumber berada pada potensi tinggi, maka anda akan mendapat nilai negatif. Jadi, transistor PMOS mempunyai nilai Vth negatif.

Proses Fabrikasi PMOS

Langkah-langkah yang terlibat dalam fabrikasi transistor PMOS dibincangkan di bawah.

Langkah 1:

Lapisan wafer silikon nipis ditukar kepada bahan jenis N dengan hanya mendopan bahan fosforus.

Langkah 2:

Lapisan Silikon dioksida (Sio2) tebal ditanam pada substrat jenis-p yang lengkap.

Langkah 3:

Kini permukaannya disalut dengan photoresist di atas lapisan silikon dioksida yang tebal.

Langkah 4:

Selepas itu, lapisan ini hanya terdedah kepada cahaya UV melalui topeng yang mentakrifkan kawasan-kawasan di mana penyebaran akan berlaku bersama-sama dengan saluran transistor.

Langkah 5:

Kawasan ini terukir bersama dengan silikon dioksida yang mendasari supaya permukaan wafer terdedah dalam tingkap yang ditentukan oleh topeng.

Langkah 6:

Baki photoresist ditanggalkan & lapisan Sio2 nipis ditanam biasanya 0.1 mikrometer di seluruh permukaan cip. Selepas itu, polysilicon diletakkan di atas ini untuk membentuk struktur pintu pagar. Photoresist diletakkan di atas seluruh lapisan polysilicon & mendedahkan cahaya UV melalui topeng2.

Langkah 7:

Resapan dicapai melalui pemanasan wafer ke suhu maksimum & melepasi gas dengan kekotoran jenis p yang dikehendaki seperti Boron.

Langkah 8:

Silikon dioksida setebal 1 mikrometer ditanam & bahan photoresist dimendapkan di atasnya. Dedahkan cahaya ultraungu dengan topeng3 pada kawasan pilihan pintu pagar, sumber & longkang yang terukir untuk membuat sambungan terputus.

Langkah 9:

Kini logam atau aluminium dimendapkan di atas permukaan ketebalan 1 mikrometernya. Sekali lagi bahan photoresist ditanam di seluruh logam & mendedahkan cahaya UV melalui mask4 yang terukir untuk membentuk reka bentuk interkoneksi yang diperlukan. Struktur PMOS akhir ditunjukkan di bawah.

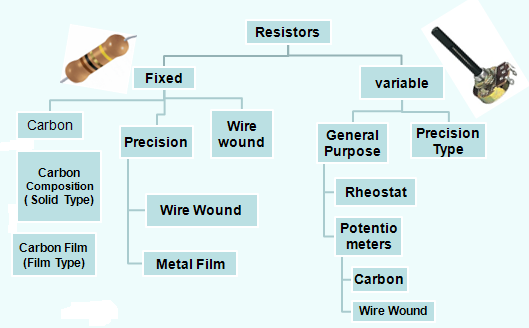

Ciri-ciri Transistor PMOS

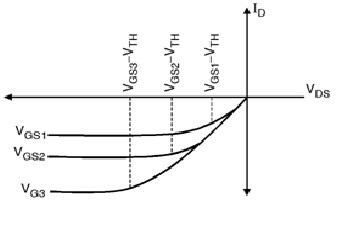

Ciri transistor PMOS I-V ditunjukkan di bawah. Ciri-ciri ini dibahagikan kepada dua kawasan untuk mendapatkan hubungan antara longkang dengan arus punca (I DS) serta voltan terminalnya seperti kawasan linear & tepu.

Di kawasan pelapik, IDS akan meningkat secara linear apabila VDS (voltan longkang ke sumber) dinaikkan manakala di kawasan tepu, I DS adalah stabil & ia bebas daripada VDS. Hubungan utama antara ISD (sumber untuk mengalirkan arus) & voltan terminalnya diperolehi oleh prosedur serupa transistor NMOS. Dalam kes ini, satu-satunya perubahan ialah pembawa caj yang terdapat dalam lapisan penyongsangan hanyalah lubang. Apabila lubang bergerak dari punca ke longkang maka pengaliran arus juga sama.

Oleh itu, tanda negatif muncul dalam persamaan semasa. Di samping itu, semua bias yang digunakan pada terminal peranti adalah negatif. Jadi, ciri ID transistor PMOS - VDS ditunjukkan di bawah.

Persamaan arus longkang untuk transistor PMOS di kawasan linear diberikan sebagai:

ID = – mp Cox

Begitu juga, persamaan arus longkang untuk transistor PMOS dalam kawasan tepu diberikan sebagai:

ID = – mp Cox (VSG – | V TH |p )^2

Di mana 'mp' ialah mobiliti lubang & '|VTH| p’ ialah voltan ambang transistor PMOS.

Dalam persamaan di atas, tanda negatif akan menunjukkan bahawa ID( arus longkang ) mengalir dari longkang (D) ke punca (S) manakala lubang mengalir ke arah yang bertentangan. Apabila mobiliti lubang adalah rendah berbanding dengan mobiliti elektron maka transistor PMOS mengalami keupayaan pemacu arus rendah.

Oleh itu, ini adalah mengenai gambaran keseluruhan transistor PMOS atau transistor mos jenis p – fabrikasi, litar dan cara kerjanya. PMOS transistor direka bentuk dengan p-sumber, n-substrat & longkang. Pembawa caj PMOS adalah lubang. Transistor ini mengalir sebaik sahaja voltan rendah digunakan pada terminal get. Peranti berasaskan PMOS kurang terdedah kepada gangguan berbanding peranti NMOS. Transistor ini boleh digunakan sebagai perintang terkawal voltan, beban aktif, cermin arus, penguat trans-impedans, dan juga digunakan dalam suis dan penguat voltan. Berikut adalah soalan untuk anda, apakah transistor NMOS?